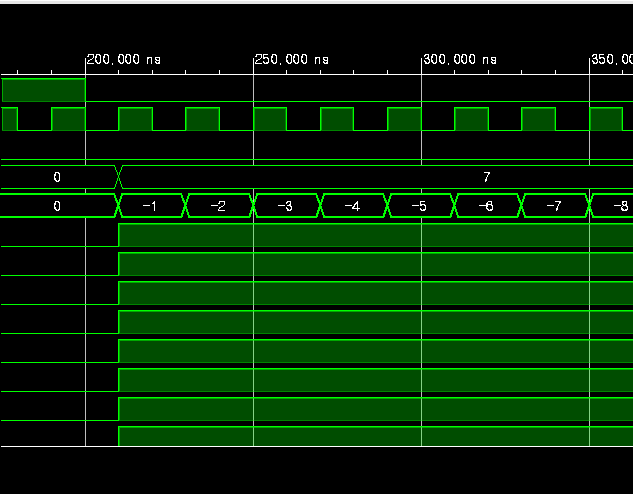

[2024.04.12.금] 인천인력개발원 하만 세미콘 아카데미 Verilog를 이용한 RTL 시스템 반도체 설계 시스템 작업(System Tasks) 1. System Tasks: 미리 작성된 코드의 모음 Simulation Tasks: 가시성과 디버깅 향상 Operations: 콘솔에 출력 / net의 값 모니터링 / 시뮬레이션 시작,정지 $로 시작 Verilog에서 타이밍 체크 2. System Tasks 예시 $display: 콘솔에 값 출력 ex. $display("At time %d, q = %b", $time, q); $time, $realtime: 현재의 시뮬레이션 시간을 정수로 표현 $wirte: $display와 유사하나 새로운 줄을 자동으로 추가 x $write ("Simulation ..