728x90

1. 논리 회로 출력값(Output) 구하기

- 부울 표현의 연산 규칙

- 괄호를 제외한 변수의 모든 역변환 수행

- 괄호 내의 연산 수행

- AND 연산 후 OR 연산 수행

- 연산식에 바(NOT)가 있으면 내부 연산 수행 후 결과 역변환

- 부울 연산 예시

- AND, OR, NOT 게이트를 이용한 논리회로에서의 Input에 따른 결과값 예시

2. NOR게이트와 NAND게이트

1. NOR 게이트

- NOR 게이트의 결과값은 OR연산 수행 후 NOT연산을 진행하여 계산 가능

- NOR 게이트 = NOT OR(OR 결과에 Inversion을 나타내는 Bubble 표시)

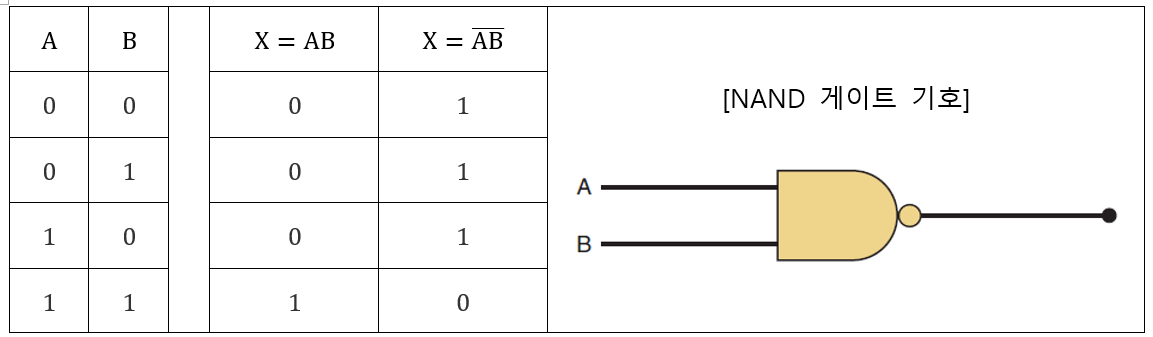

2. NAND 게이트

- NAND 게이트의 결과값은 AND연산 수행 후 NOT연산을 진행하여 계산 가능

- NAND 게이트 = NOT AND(AND 결과에 Inversion을 나타내는 Bubble 표시)

3. Boolean Theorems & DeMorgan's Theorem

- 논리 연산의 표현과 논리회로를 간단하게 하는 방법

- DeMorgan's Theorems

4. NAND 게이트와 NOR 게이트의 범용성(Universality)

1. NAND 게이트를 통해 INVERTER, AND, OR 게이트 구현 가능

2. NOR 게이트를 통해 INVERTER, AND, OR 게이트 구현 가능

5. 논리 게이트의 대안 논리기호

- 대안 논리 기호 변환 방법

- 모든 입출력을 역변환(Inversion Bubble이 있는 곳에서는 bubble 제거, 없던 곳에 bubble 추가)

- 연산기호를 AND에서 OR로, OR에서 AND로 변환

- 대안 논리 기호 변환 예시

- 대안 논리기호 특징

- 등가성은 입력단자의 수가 많을 때도 성립

- 표준기호는 입력에 버블이 없으나 모든 대안기호에는 버블 존재

- 표준기호와 대안기호로 이루어진 회로는 모두 같은 회로 표현

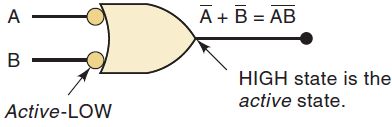

- Active HIGH / Active LOW

- Active HIGH: Input이나 Output에 버블(Inversion)이 없는 신호

- Active LOW: Input이나 Output에 버블(Inversion)이 있는 신호

- 예시1: 모든 Input이 HIGH일 때만 Output이 LOW가 됨 -> Output이 LOW일 때 active 상태(Active LOW)

- 예시2: 한 개의 Input이라도 LOW면 Output이 HIGH가 됨 -> Output이 HIGH일 때 active 상태(Active HIGH)

6. 전파 지연(Propogation Delay)

- 전파 지연: 시스템에서 Input을 받은 후 Output을 생성하기까지의 시간차

- 실제 신호의 천이: 직각으로 변하는 것이 아닌 서서히 LOW-HIGH로, HIGH-LOW로 천이

- 측정 기준: Input의 50%지점과 Output의 50%지점 간의 시간 간격을 통해 측정

- t_PLH: 신호가 LOW에서 HIGH로 가는 데 걸리는 시간

- t_PHL: 신호가 HIGH에서 LOW로 가는 데 걸리는 시간

728x90

'자습시간 > 디지털 논리회로' 카테고리의 다른 글

| Chap 04_1. SOP 형태 / POS 형태 / 논리회로 단순화 / 대수적 단순화 / 조합 논리회로 / Karnauph map(K-map) (4) | 2024.04.07 |

|---|---|

| Chap 03_1. 부울 상수 / 부울 변수 / 진리표 / 논리게이트(AND, OR, NOT) (5) | 2024.03.23 |

| Chap 02. 진수 변환 / BCD 코드 / Gray 코드 (4) | 2024.03.23 |

| Chap 01. 기초 개념 (1) | 2024.03.23 |