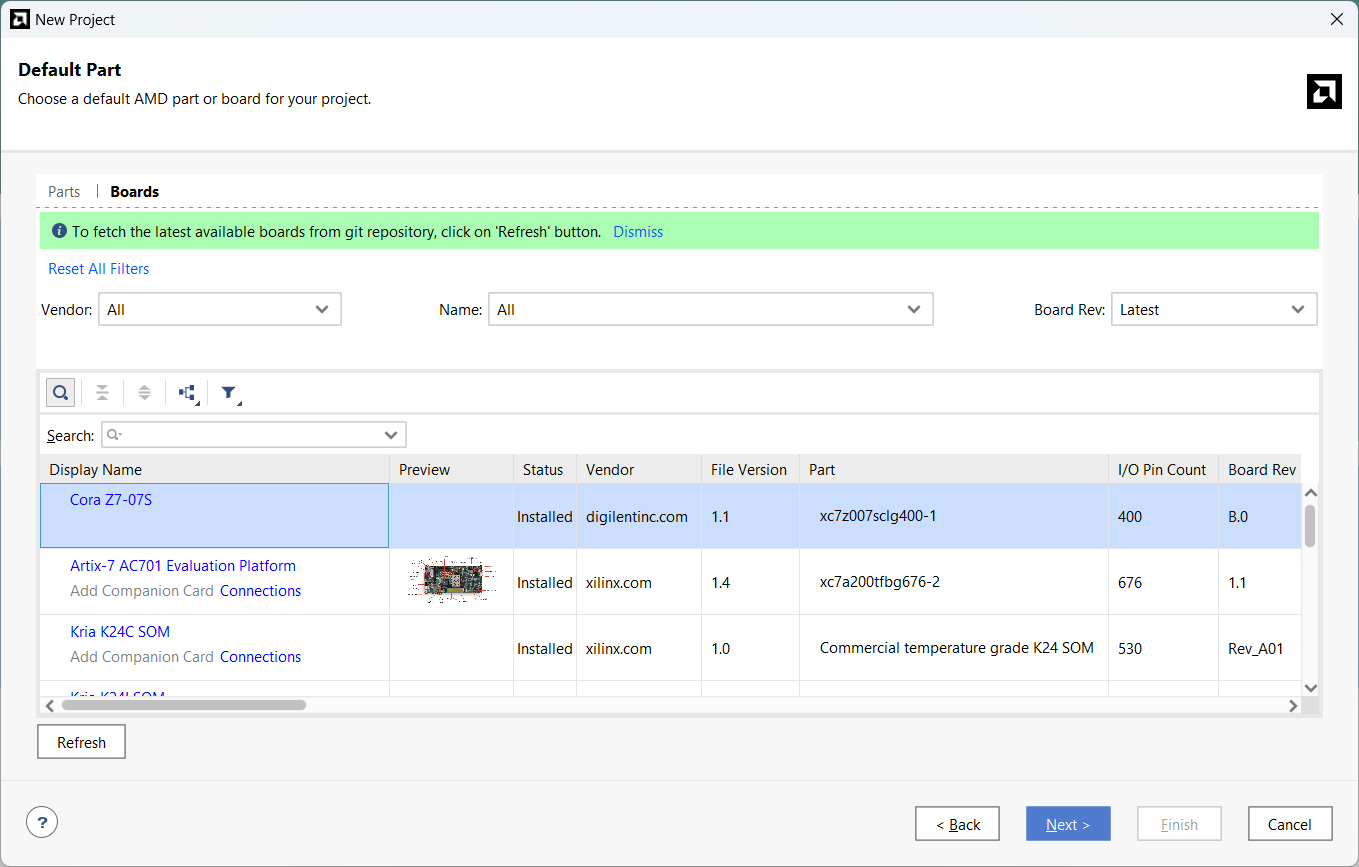

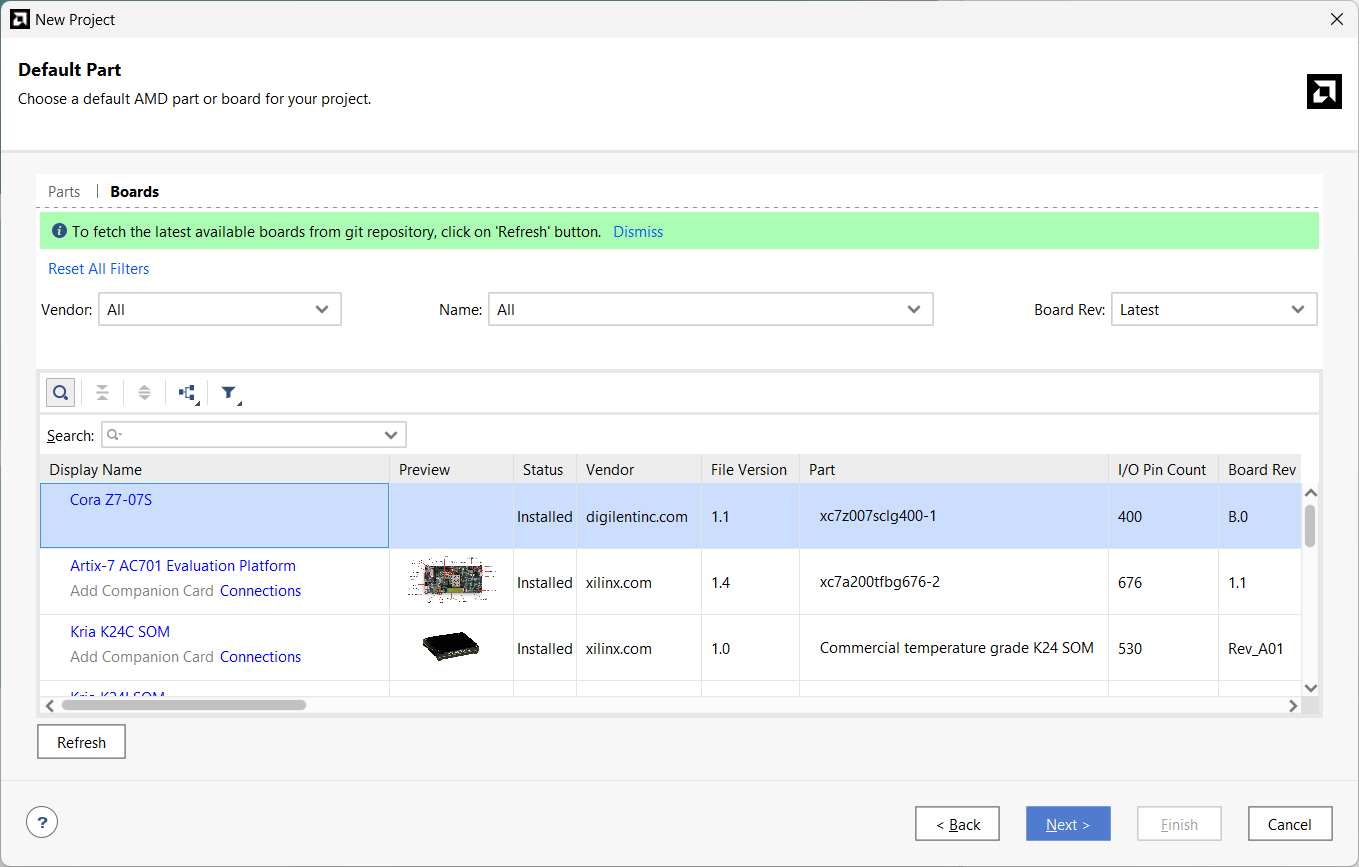

1. New Project 생성 - Source 추가: 전 과정에서 생성된 myip2_slave_lite_v1_0_S00_AXI.v 파일, segment 출력 파일 2. 보드 선택 후 finish 3. myip2_slave~~.v에서 segment와 연결하기 위한 hi_bit과 low_bit을 output으로 선언 4. myip2_slave~~.v에서 output으로 나갈 high bit와 low bit에 slave의 register 값을 나누어 할당 5. Create Block Desgin - Zynq 추가 - Run Block Automation 6. Zynq7의 Ethernet, USB 포트 비활성화 7. PS/PL Interface 확인 8. Add module - 모듈 추가 9. Run ..