728x90

[2024.04.11.목] 인천인력개발원 하만 세미콘 아카데미

전자회로 해석 및 설계

3-1. 댐핑저항

- 댐핑저항

- 댐핑저항이 클수록 공진 감소

- LC filter에서 LC 공진에 의한 Peaking 대역 존재

- 방지를 위해 직렬 저항 구성

- 댐핑저항 선택 방법: 수Ω~100Ω 내의 저항 사용(주로 20Ω~30Ω)

- PCB에서 기생L, C에 의한 공진, 전자파 발생을 줄이기 위해 댐핑저항 설치

1. 댐핑 저항 10mΩ 설치

2. 100mΩ 설치

3. 댐핑저항 1kΩ 설치, maximum step size 30u으로 변경

4. 댐핑저항 3Ω

5. 프로필ac로 변경, 입력을 AC로 변경하기 위해 PULSE 더블클릭, AC칸에 1 입력

6. 시뮬레이션 실행

7. 댐핑저항 제거 후 다시 시뮬레이션

- 전송선로: 신호가 지나가는 길

- 공진주파수가 높아져야 고속신호처리가 가능

- 파워 라인은 DC-> 저주파이므로 공진주파수가 더 낮아도 큰 문제 X

- LC 공진(LC Resonance)

- X_C와 X_L이 같아지는 주파수

- 직렬 공진 임피던스 0Ω

- 병렬 공진 임피던스 ∞Ω

- 댐핑저항(LC공진 대책)

- LC filter에서 LC 공진에 의한 peaking 대역 존재(위 실습에서 뾰족하게 솟아있는 부분)

- peaking 대역을 방지하기 위해 직렬 저항 구성

용어 정리

KC: Korea Certification(한국인증)

FC: Federal Certificate(미국인증)

CE: Conformité Européene(유럽인증)

1. SI & PI

- Integrity: 무결성. 전자회로에서 전송되는 신호, 데이터가 안정적으로 전달되는 척도

-

SI(Signal Integrity): 신호 무결성

-

송신 신호가 왜곡 없이 수신기로 전달되는 정도

-

신호 고속화에 따라 신호의 반사, 지연, 손실 등의 문제로 인해 발생

-

VNA, TDR등으로 신호 무결성 측정 가능

-

Damping 저항 추가로 향상 가능

-

- PI(Power Integrity): 전원 무결성

- 신호가 안정적으로 송수신되기 위해 전류가 안정적으로 유지되는 정도

- 주로 과전류가 채널 인덕턴스와 반응하며 생성

- EMI문제 식별을 통해 분석 가능

2. EMI & EMS & EMC

- EM-: Electro-Magnetic- (전자- 또는 전자기-)

-

EMI(Electro-Magnetic Interference) – 법적 제한(KC인증-전파인증마크)

-

전자기 간섭 / 방해

-

장치의 동작으로 인해 노이즈의 발생 정도 및 주변 IC, 시스템에 미치는 영향에 대한 지표

-

Damping 저항 추가로 향상(EMI 감소) 가능

- 측정방법: EMI Chamber (ex. SGS S. A.)

-

- EMS(Electro-Magnetic Susceptibility)

- 전자기 내성

- 외부 노이즈의 영향을 받아도 오동작을 일으키지 않는 내성에 대한 지표

- EMC(Electro-Magnetic Compatibility)

- 전자파 적합성

- 특정 기기가 다른 기기를 간섭하지도, 다른 기기로부터 간섭을 받지도 않는 성질

- EMI와 EMS를 포괄하는 개념(낮은 EMI, 높은 EMS -> 높은 EMC)

3-2. 현업 용어정리 / LC공진 / 비즈 / 커플링 캐패시터

- 캐패시터 구성: 자체 캐패시턴스+회로에 존재하는 기생저항, 기생 인덕터

- ESR(Equivalent Series Resistance): 기생저항의 합

- ESL(Equivalent Series Inductance): 기생 인덕턴스의 합

- SRF(Self Resonance Freq.) : Self 공진주파수, SRF가 신호 주파수의 3배 이상 선호

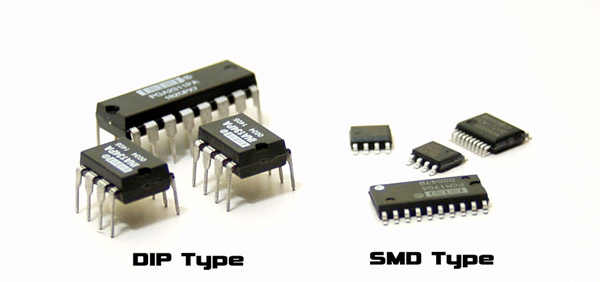

2. DIP(Dual In-line Package)type & SMD(Surface Mounted Device) type & BGA(Ball Grid Array) type

- DIP type -> 길이 증가 -> ESL 증가 -> SRF 감소 -> 고속동작 불리

- SMD type -> 길이 감소 -> ESL 감소 -> SRF 증가 -> 고속동작 유리

- BGA: 칩 내의 길이를 최소화하여 SMD보다 더 고속 처리가 가능한 형태

- PLP(panel level packaging): 초고속 동작 영역에 사용(AP 등)

3. Beads(비즈)

- 공진이 잘 일어나지 않는 인덕터(인덕터는 코어 저항=R_par을 크게하여 공진 이용)

- Beads의 동작 특성

- 직류 입력 -> L_bead가 short효과 -> 임피던스 Zbeads = R_series

- 주파수 증가 -> L_bead에 의해 임피던스 증가 -> Zbeads = jωL_bead + R_series

- LC 공진 영역에서 임피던스 무한대 -> Zbeads = R_par + R_series

- 1GHz 이상의 고주파 영역: C_par의 임피던스 감소 -> Zbeads = 1/jωC+R_series

출처: element14 Community

- 비즈 회로 응용 예시: Switching Regulator 바로 옆에 Beads 설치하여 노이즈 최소화 가능

위 회로에서는 디지털 회로에 의해 아날로그 회로에 간섭 발생 가능

- 위 회로에서 디지털 회로와 아날로그 회로간 간섭(노이즈)를 제거하기 위해 파워 분리 사용

파워 분리: 위와 같이 비즈를 이용하여 회로를 분할하는 것을 파워분리라 함

- 위 회로에서 디지털 회로와 아날로그 회로간 간섭(노이즈)를 제거하기 위해 파워 분리 사용

4. 커플랭 캐패시터(Coupling Capacitor)

- Coupling C의 특성

- DC차단, AC 통과

- C가 AC-Coupling, DC-Decoupling의 역할

- Coupling C는 직류를 분리하고 교류를 통과시키는 용도이므로 대체로 1uF 이상의 큰 용량 사용

728x90