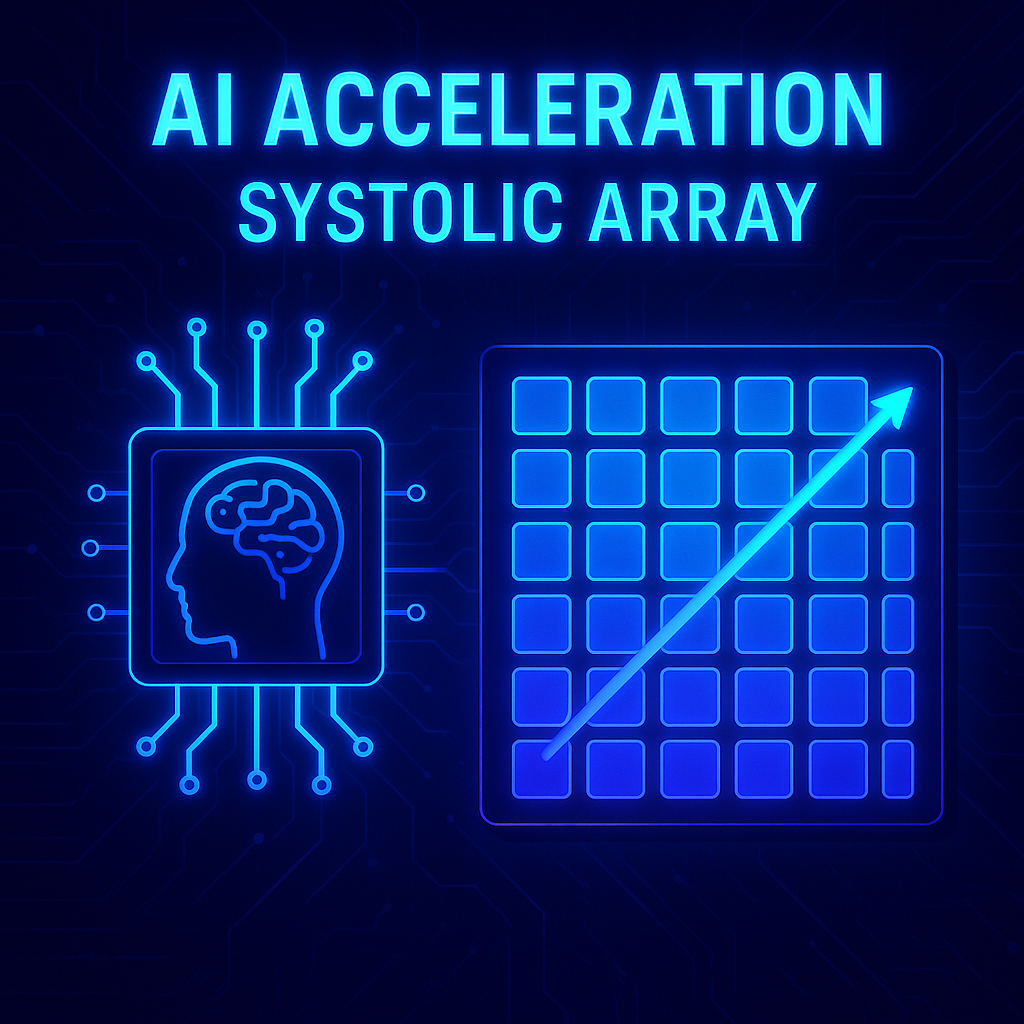

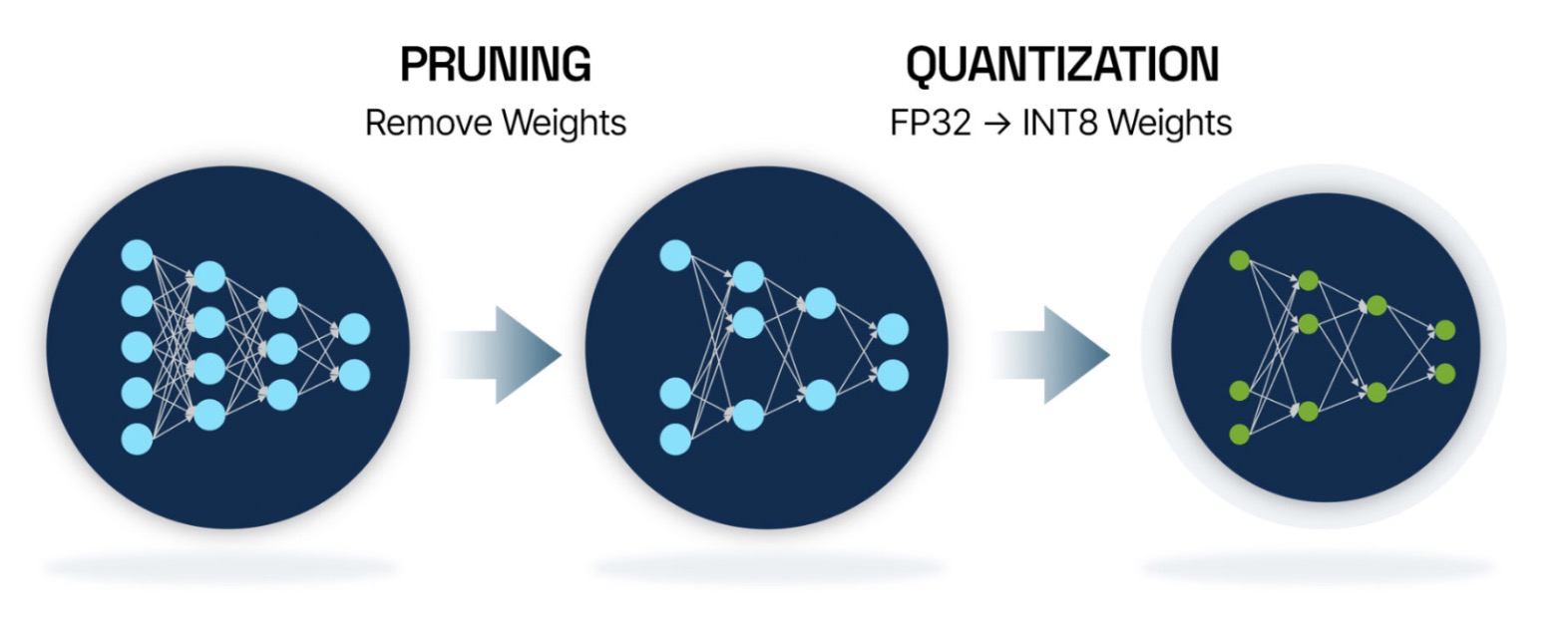

STRAIT(3) _ Self-DiagnosisSTRAIT(2) _ BIST(Built-In Self Test)STRAIT(1) _ AI 가속기의 자가 테스트 및 복구 기술이번 포스팅은『STRAIT: Self-Test and Self-Recovery Architecture for Systolic-Array-Based AI Accelerators』 논문을 바탕으로 제작되었습니semicon-circuit.tistory.comSystolic Array 기반 AI 가속기에서는 수천 개의 PE(Processing Element)가 고속 병렬 연산을 수행합니다. 하지만 그 중 일부가 고장나면 전체 연산에 영향을 줄 수 있기 때문에, 결함 복구(Self-Recovery) 기술이 필수적입니다. STRAIT는 Built..