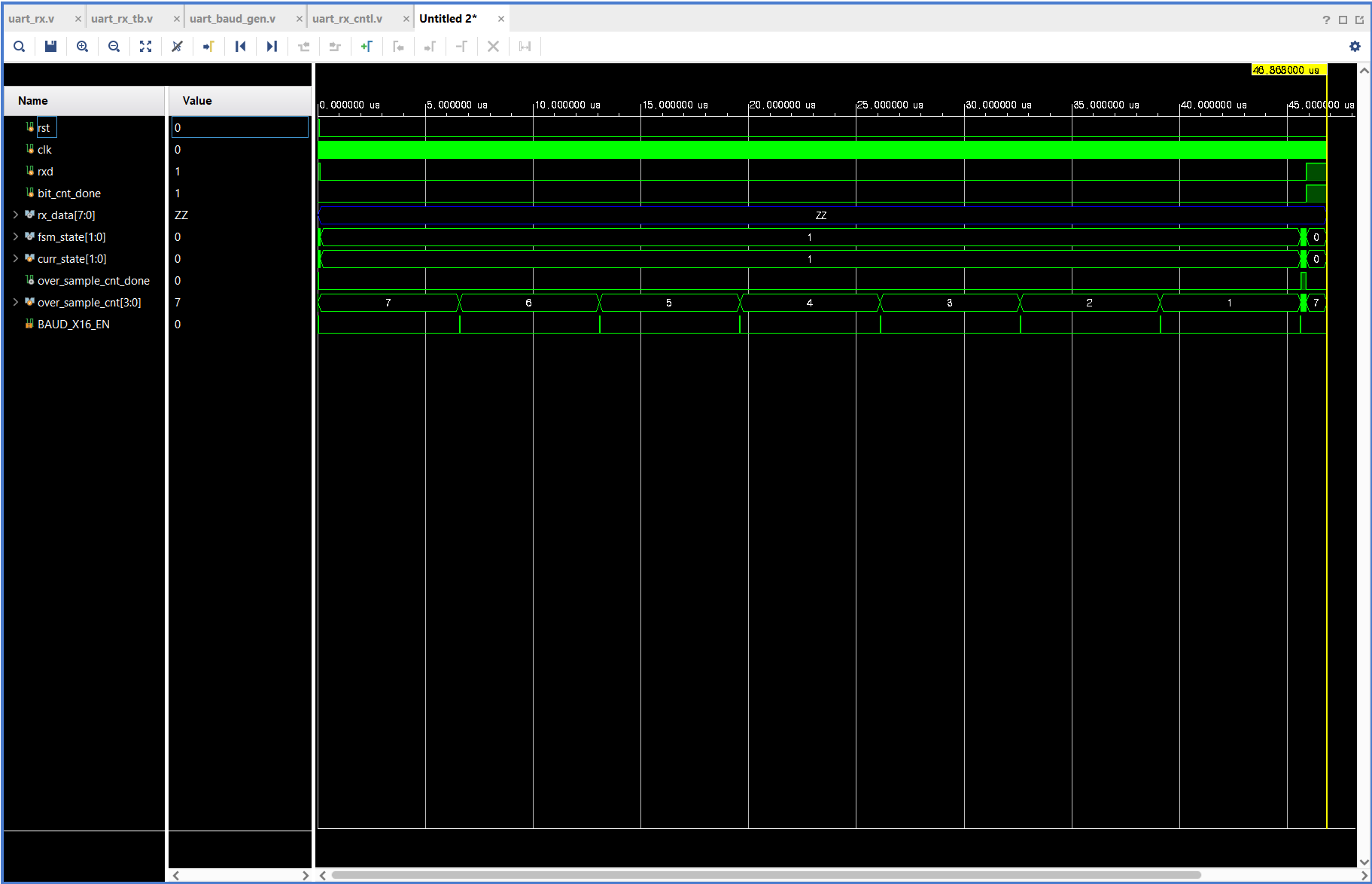

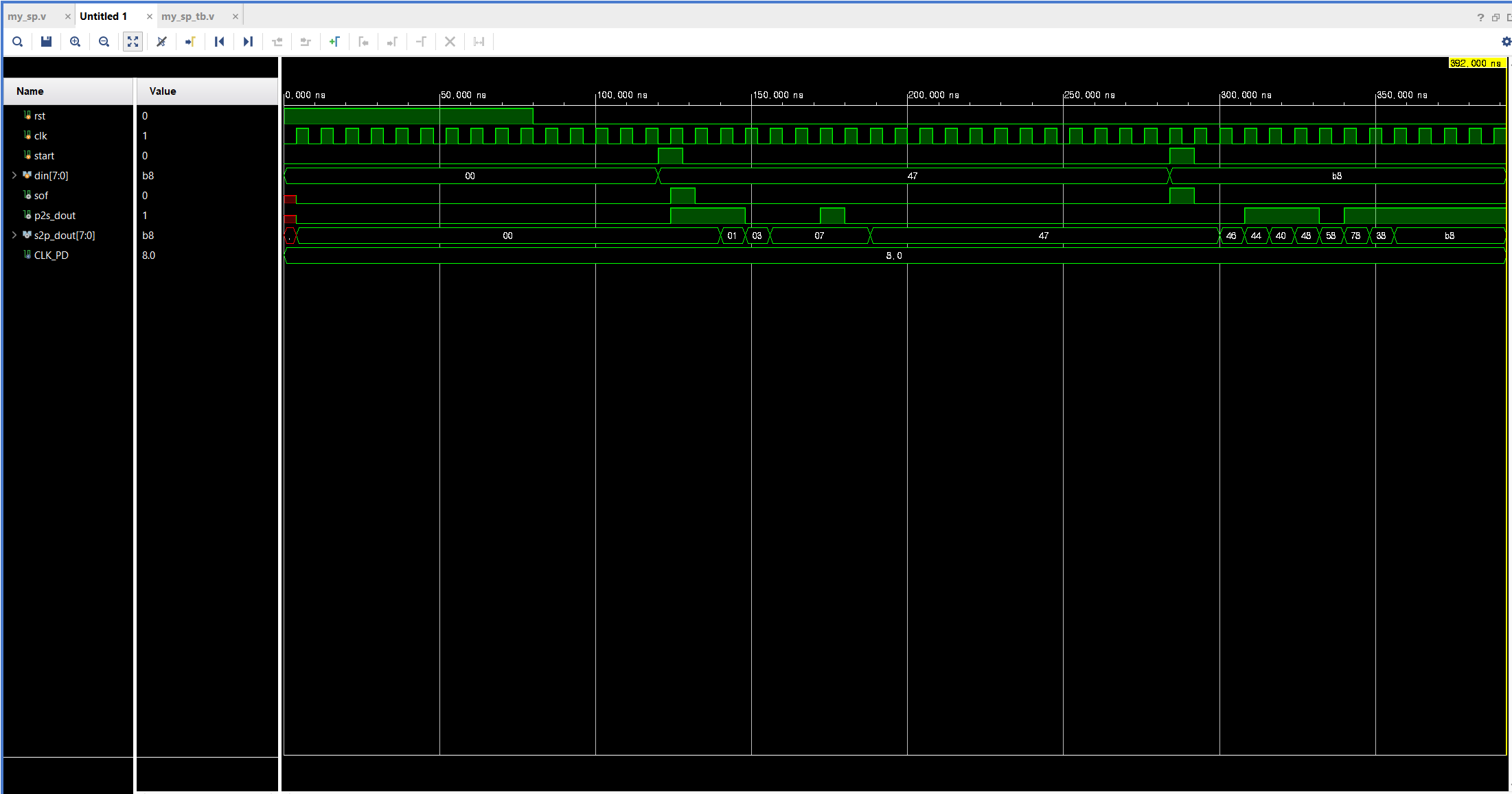

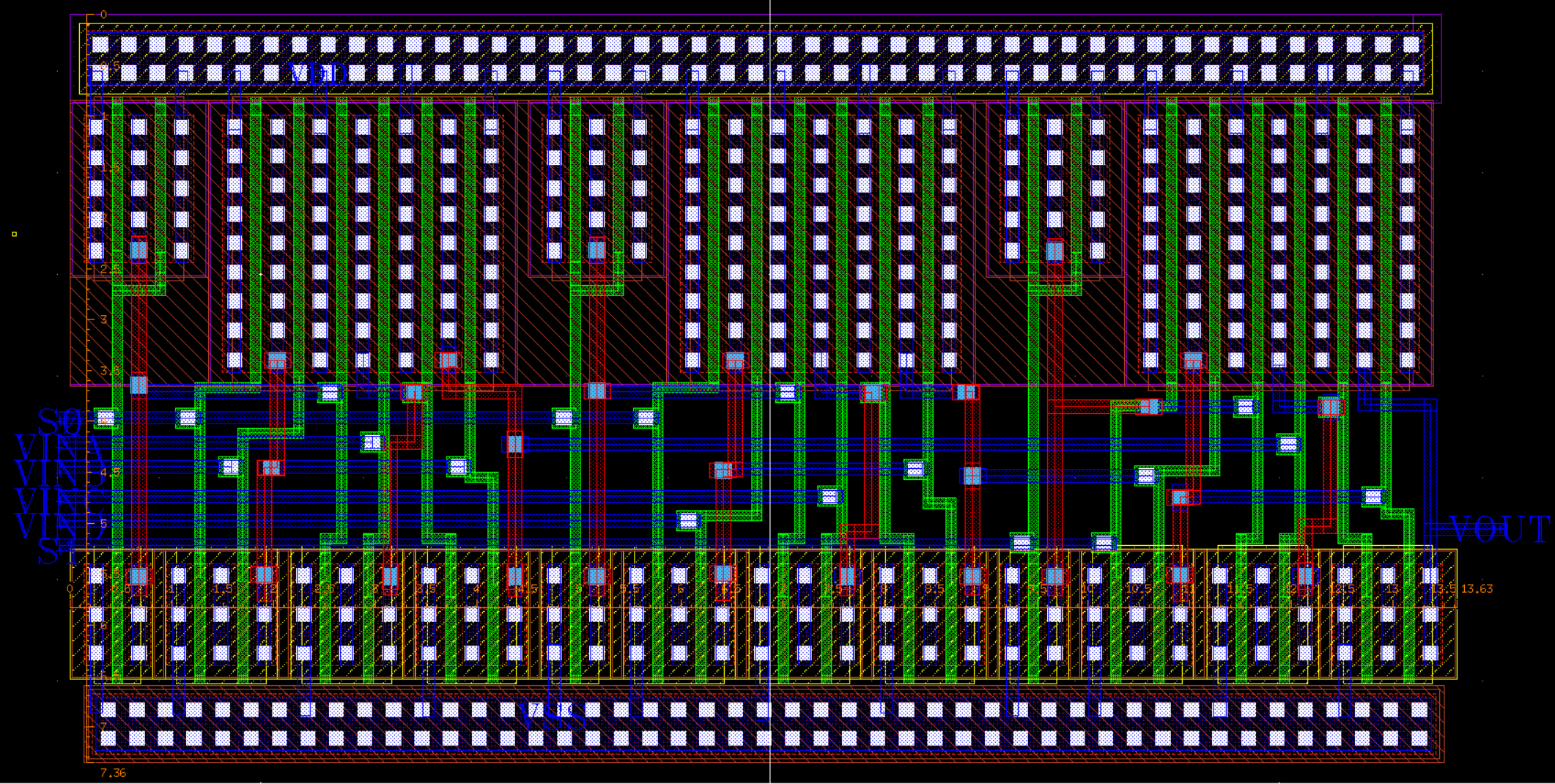

[2024.05.20.월] 인천인력개발원 하만 세미콘 아카데미실습 1: uart_rx1. uart_rx_cntl.v Design Sources 생성 2. 코드 작성`timescale 1ns / 1ps//////////////////////////////////////////////////////////////////////////////////// Company: // Engineer: // // Create Date: 2024/05/20 12:06:26// Design Name: // Module Name: uart_rx_cntl// Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Re..