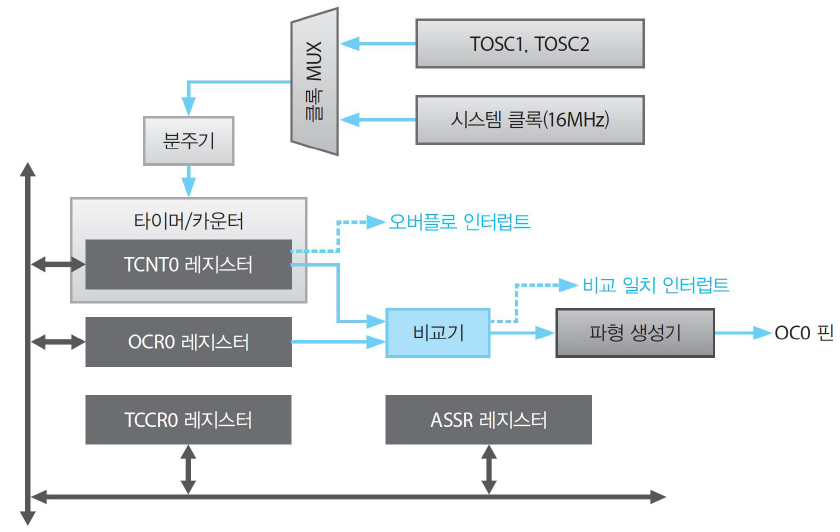

[2024.03.28.목] 인천인력개발원 하만 세미콘 아카데미임베디드 시스템을 위한 SW 구조설계8비트 타이머 / 카운터1. 타이커/카운터 인터럽트 현재까지의 펄스 수: TCNTn레지스터에 저장 오버플로 인터럽트 최대로 셀 수 있는 펄스 이상이 되면 TCNTn레지스터가 0으로 바뀌며 발생 비교일치 인터럽트 TCNTn의 값이 미리 설정된 OCRn레지스터값과 일치하면 발생 2. TCCR0 레지스터: 분주비 설정CLK 주파수: 16,000,000HzTCNT는 최대 256, TCCR은 16 -> 256*26 = 4096 (≒4K)TCCR이 64면 16K -> 16KHz가 ATmega의 최대 주파수따라서 분주비를 64로 설정 3. TIMSK 레지스터: 인터럽트 활성화EIMSK: External Input Mask..