728x90

[2024.05.17.금] 인천인력개발원 하만 세미콘 아카데미

실습 1: Parallel to Serial / Serial to Parallel 변환기

1. my_sp 프로젝트 생성

2. my_sp.v 파일을 Create Design Sources로 생성한 뒤 코드 작성(my_p2s와 my_s2p 모듈 두 개 사용)

`timescale 1ns / 1ps

/********************************************

parallel to serial

********************************************/

module my_p2s (input RST, CLK, START,

input [7:0] DIN,

output SOF,

output DOUT

);

reg [2:0] bit_cnt;

assign DOUT = DIN[bit_cnt];

assign SOF = bit_cnt == 3'd0;

always @(posedge CLK)

begin

if(RST)

bit_cnt <= 3'd7;

else if(START)

bit_cnt <= 3'd0;

else if(bit_cnt < 3'd7)

bit_cnt <= bit_cnt + 1;

end

endmodule

/********************************************

serial to parallel

********************************************/

module my_s2p (input RST, CLK, SOF,

input DIN,

output reg [7:0] DOUT

);

reg [2:0] bit_cnt;

reg data_reg;

always @(posedge CLK)

begin

if(RST) begin

DOUT <= 8'd0;

data_reg <= 1'b0;

end else begin

DOUT[bit_cnt] <= data_reg;

data_reg <= DIN;

end

end

always @(posedge CLK)

begin

if(RST)

bit_cnt <= 3'd7;

else if(SOF)

bit_cnt <= 3'd0;

else if(bit_cnt < 3'd7)

bit_cnt <= bit_cnt + 1;

end

endmodule

3. 테스트벤치를 위해 Create Simulation Sources - my_sp_tb.v파일 생성 후 코드 작성

`timescale 1ns / 1ps

module my_sp_tb( );

parameter CLK_PD = 8.0;

reg rst, clk, start;

reg [7:0] din;

wire sof;

wire p2s_dout;

wire [7:0] s2p_dout;

my_p2s uut_0 (.RST (rst), .CLK (clk), .START (start),

.DIN (din),.SOF (sof),.DOUT (p2s_dout) );

my_s2p uut_1 (.RST(rst), .CLK(clk), .SOF(sof),

.DIN (p2s_dout), .DOUT (s2p_dout) );

initial begin

rst = 1'b1;

#(CLK_PD*10);

rst = 1'b0;

end

initial clk = 1'b0;

always #(CLK_PD/2) clk = ~clk;

initial begin

start = 1'b0;

din = 8'd0;

wait (rst == 1'b0);

#(CLK_PD*5);

start = 1'b1;

din = 8'h47;

#(CLK_PD);

start = 1'b0;

repeat (20) @(posedge clk);

start = 1'b1;

din = 8'hb8;

#(CLK_PD);

start = 1'b0;

#100;

$finish;

end

endmodule

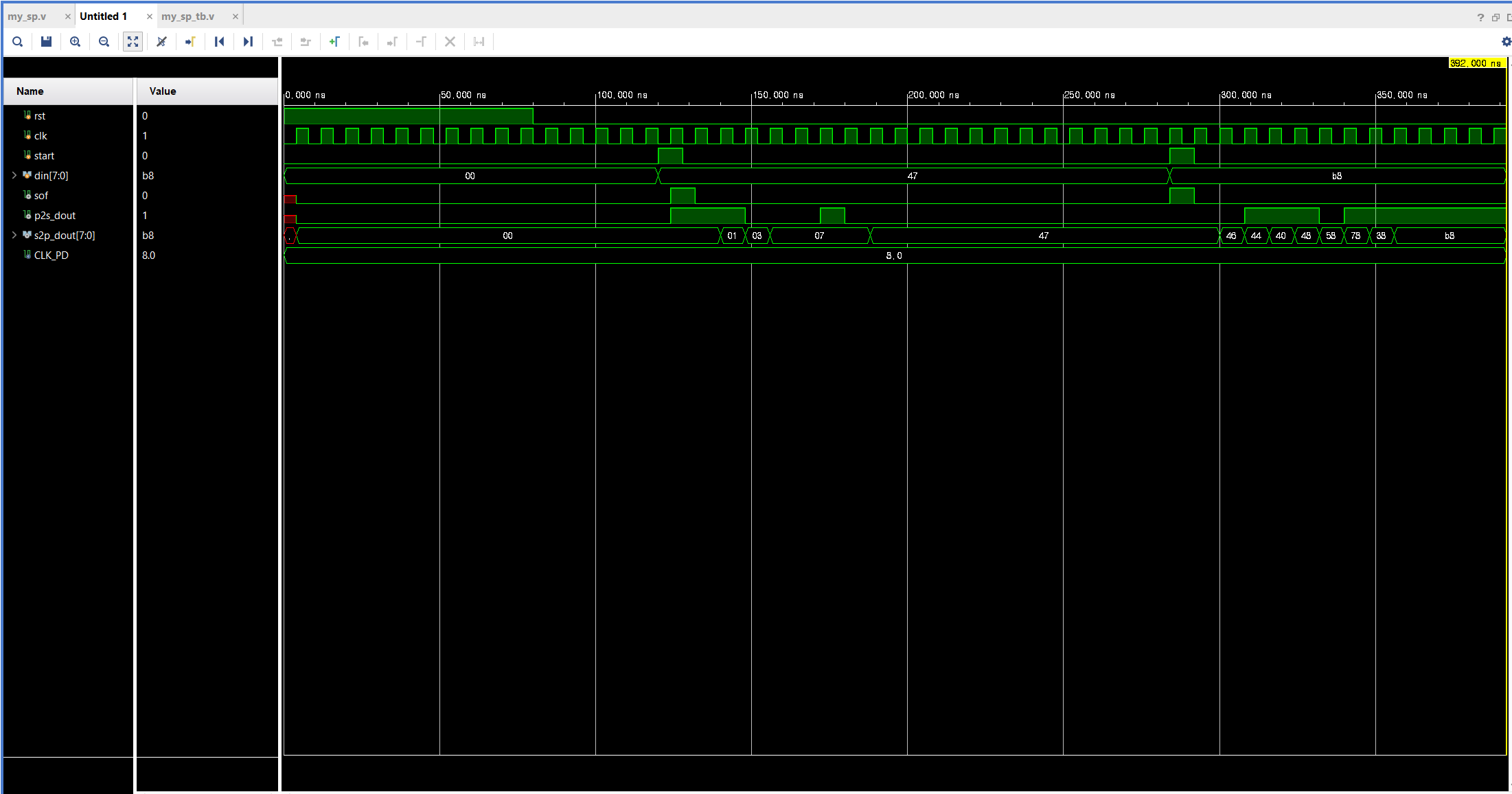

4. Behavioral Simualtion 진행 후 파형 확인

실습 2: Uart_rx

1. my_uart 프로젝트 생성

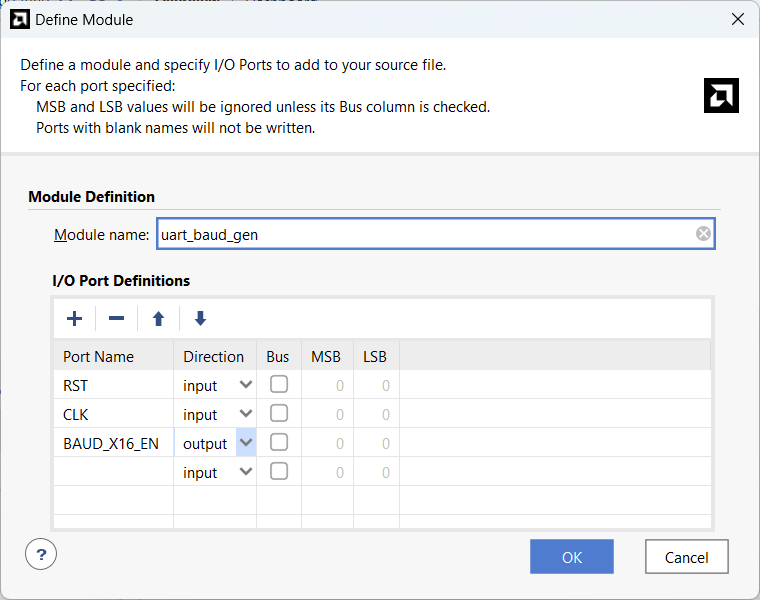

2. Add or Create Design Sources - Create File - uart_baud_gen.v 생성 후 포트 정의

3. 코드 작성

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2024/05/17 15:27:03

// Design Name:

// Module Name: uart_baud_gen

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module uart_baud_gen(

input RST,

input CLK,

output BAUD_X16_EN

);

parameter CLK_FREQ = 125_000_000;

parameter BAUD_RATE = 9600;

localparam MAX_CNT = CLK_FREQ / (BAUD_RATE * 16);

reg [12:0] cnt;

reg enable;

assign BAUD_X16_EN = enable;

always @(posedge CLK)

begin

if(RST) begin

cnt <= 13'd0;

enable <= 1'b0;

end else begin

if (cnt == (MAX_CNT-1)) begin //cnt가 0부터 시작하므로 MAX_CNT - 1까지 해야 수가 맞음

cnt <= 13'd0;

enable <= 1'b1;

end else begin

cnt <= cnt + 1;

enable <= 1'b0;

end

end

end //always

endmodule4. Simulation을 위해 Add or Create Simulation sources - Create File로 uart_baud_gen_tb.v파일 생성

5. 코드 작성

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2024/05/17 16:03:20

// Design Name:

// Module Name: uart_baud_gen_tb

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module uart_baud_gen_tb();

parameter CLK_PD = 8.0;

reg rst, clk;

wire enable;

uart_baud_gen uut( //포트 맵핑

.RST (rst),

.CLK (clk),

.BAUD_X16_EN (enable)

);

initial begin

rst = 1'b1;

#(CLK_PD*10);

rst = 1'b0;

end

initial clk = 1'b0;

always #(CLK_PD/2) clk = ~clk;

endmodule

6. simulation 결과 확인

728x90

'하만(Harman) 세미콘 반도체 설계 과정 > Verilog를 이용한 RTL 시스템 반도체 설계' 카테고리의 다른 글

| 하만(Harman) 세미콘 아카데미 52일차 - Verilog HDL 설계(UART 실습, RAM 설계) (0) | 2024.05.27 |

|---|---|

| 하만(Harman) 세미콘 아카데미 47일차 - Verilog HDL 설계(UART 실습) (0) | 2024.05.20 |

| 하만(Harman) 세미콘 아카데미 42일차 - Verilog HDL 설계(traffic 프로젝트 디버깅) (1) | 2024.05.10 |

| 하만(Harman) 세미콘 아카데미 37일차 - Verilog HDL 설계(FSM security, 신호등 FSM) (1) | 2024.04.29 |