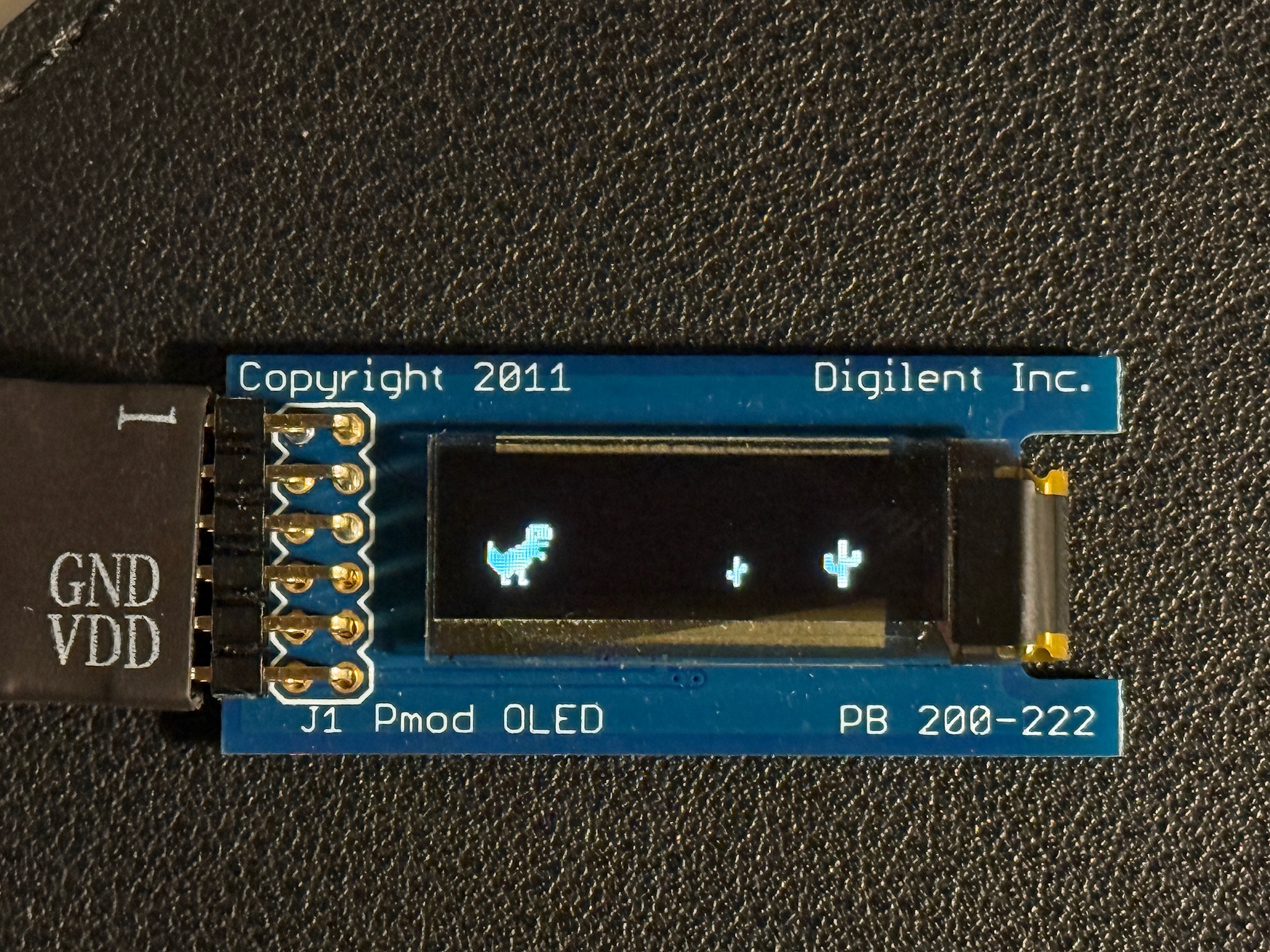

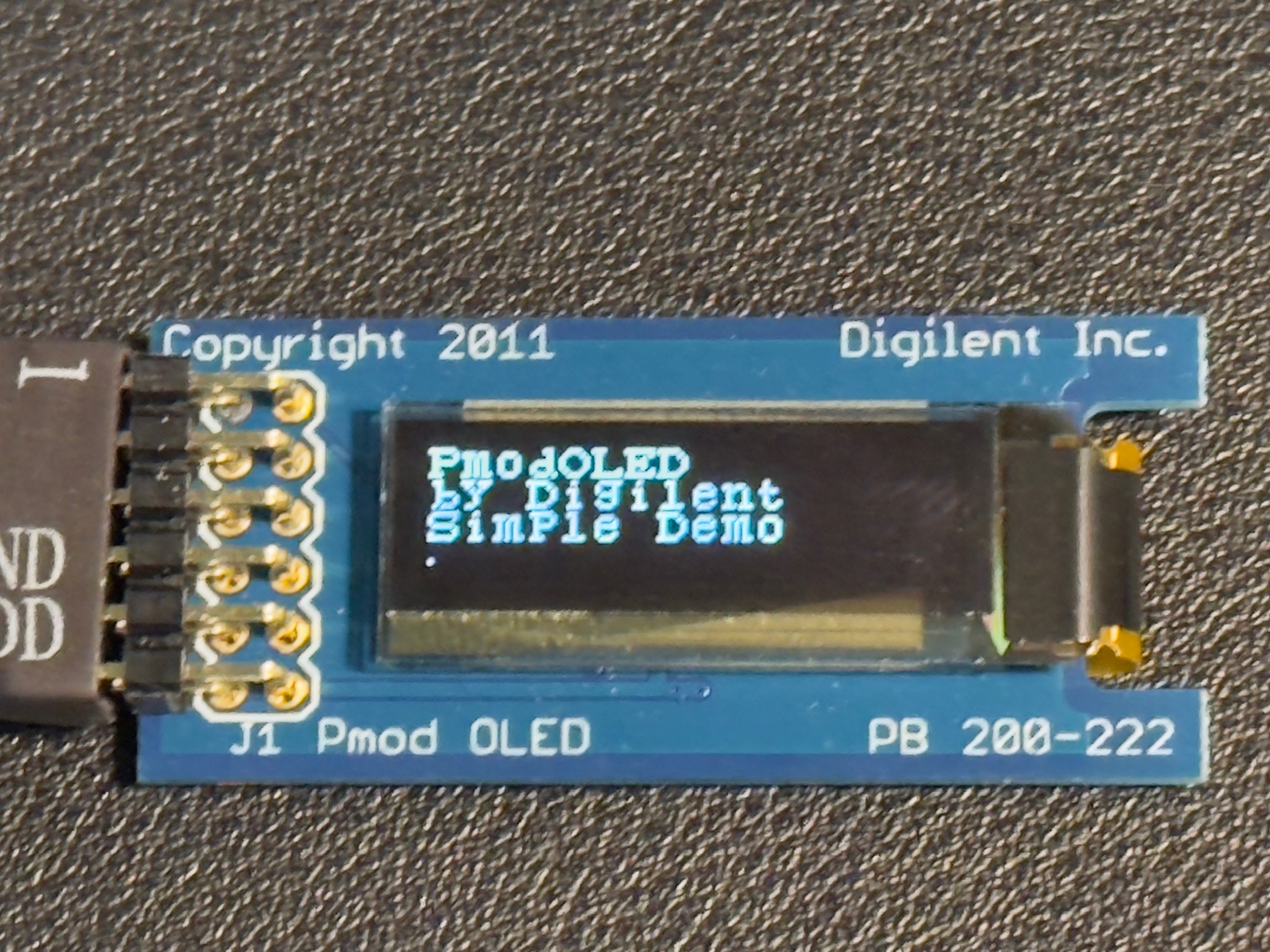

크롬 공룡 게임 구현 저번 게시글에 이어 마지막으로 Pmod KYPD와 Pmod OLED를 이용해 하드웨어 파일을 생성한 후, Vitis를 이용해 키패드로 동작하는 공룡 게임을 최종 완료했습니다. Vivado Process Vivado와 Vitis를 이용한 Pmod OLED 제어 [Pmod IP 이용]이번 게시글에서는 Digilent의 게시물과 IP 라이브러리를 통해 Pmod OLED의 데모 파일 구현을 진행합니다. 추후 이를 응용하여 Pmod OLED를 통해 다양한 기능을 구현할 예정입니다. Vivado, Vitis 이용방법semicon-circuit.tistory.com 이 게시글에서와 동일한 방법으로 Vivado Library에서 IP를 추가한 뒤, Pmod KYPD와 Pmod OLED를 추가하여 ..