[2024.03.18.월] 인천인력개발원 하만 세미콘 아카데미

Verilog를 이용한 RTL 시스템 반도체 설계

FPGA, Bit, 논리 게이트

- FPGA(Field-Programabble Gate Arrays): 하드웨어 플랫폼

- 재구성 가능: 사용자가 특정 작업을 수행하도록 구성할 수 있으며, 구성 변경도 가능

- 병렬 처리 능력: 여러 작업을 동시에 수행할 수 있는 병렬 처리 능력을 갖춤. 고속 연산이 필요한 분야에서 유리

- 낮은 지연시간: 프로세서 기반 시스템과 다르게 하드웨어 수준에서 직접 연산을 처리하므로 지연시간이 짧음

- 고성능: FPGA는 고성능을 요구하는 애플리케이션에서 ASIC의 대안으로 사용 가능하며 ASIC대비 개발 비용&시간이 적음

- 2bit <-> 8bit: 3bit씩 묶어 계산

- ex1) 10010110(2) -> (010)(010)(110)(8) = 226(8)

- ex2) 110011101(2) -> (110)(011)(101)(8) = 635(8)

- 2bit <-> 16bit: 4bit씩 묶어 계산

- ex1) 10010110(2) -> (1001)(0110)(16) = 96(16)

- ex2) 110011101(2) -> (0001)(1001)(1101)(16) = 19D(16)

- 논리 게이트

- Buffer

X OUTPUT 0 0 1 1 - NOT: 입력 반전

X OUTPUT 0 1 1 0 - AND: OUT = X * Y

X Y OUTPUT 0 0 0 0 1 0 1 0 0 1 1 1 - OR : OUT = X + Y

X Y OUTPUT 0 0 0 0 1 1 1 0 1 1 1 1 - XOR: 입력이 다를 때 1 출력

X Y OUTPUT 0 0 0 0 1 1 1 0 1 1 1 0

- Buffer

게이트 예시

- SUM(S) = (A XOR B) XOR Ci (Ci : C input)

- CARRYOUT(Co) = (A AND B) OR (Ci AND (A XOR B))

- Example 1) Full Adder

A B Ci S Co

< Full Adder >

0 0 0 0 0 1 0 0 1 0 0 1 0 1 0 1 1 0 0 1 0 0 1 1 0 1 0 1 0 1 0 1 1 0 1 1 1 1 1 1

- Example 1) Full Adder

용어 정리

- Flip-Flop(플립플롭) or Latch(래치): 1비트의 디지털 정보 저장에 사용. 주로 디지털 메로리 회로, 타이밍 회로, 상태 머신 등에서 활용됨.

- Clock(클록): 일반적으로 주기적으로 변하는 파형(대개는 사각파)으로, 디지털 회로의 여러 구성 요소가 동기화되어 작동할 수 있게 하는 타이밍 신호. 마이크로 프로세서, 메모리 장치, 다양한 디지털 시스템에서 데이터의 처리와 전송을 조정하는 데 필수적임.

- Event(이벤트)

- Edge event: 디지털 신호에서는 신호가 하나의 논리 상태에서 다른 상태로 전환하는 순간, 즉 0에서 1로 또는 1에서 0으로 바뀌는 순간을 에지 이벤트라고 함. 이는 상승 에지(0에서 1로의 전환)와 하강 에지(1에서 0으로의 전환)로 나눌 수 있다.

- 임계값 event: 아날로그 또는 디지털 신호에서, 신호의 크기가 미리 정의된 임계값을 초과하거나 미만일 때 발생. 이러한 이벤트는 센서 데이터 모니터링, 경보 시스템, 데이터 변환(예: 아날로그-디지털 변환기에서의 샘플링) 등에 사용됨.

- 주파수: 1초동안 진동하는 횟수, 단위는 Hz

- SI 단위 접두어

Introduction

[ 칩 제작 순서 ]

1. Spec 만들기 -> 검증

2. 회로도 제작(OrCAD)

3. Artwork: 보드를 제작하기 위해 각각의 부품을 배치

4. PCB 제작

5. Assembly

6. Test

- HDL(Hardware Description Language, 하드웨어 기술 언어): 디지털 시스템이나 회로를 모델링하고 설계하는 데 사용되는 컴퓨터 기반 언어

- VHDL: 미 국방성의 VHSIC(Very High-Speed Integrated Circuit) 프로그램을 통해 1980년대 초 개발. 매우 엄격한 문법을 가짐

- Verilog: 미국에서 1980년대 중반에 개발된 HDL. 문법이 C언어와 유사하며 설계와 검증이 가능

- Verilog 이용 FPGA 제작 순서

- Spec 설정

- Verilog Code

- Simulation

- Synthesis(합성): 회로도 제작 과정과 유사

- Implementation(ASIC에서 P&R): Artwork, PCB 제작 과정과 유사

- Configuration

- Test

- 실습 시 AMD의 FPGA(Cora Z7)을 Vivado 프로그램으로 설계

- amd.com - 다운로드 - FPGA 및 적응형 SoC에서 Vivado ML 개발자 툴을 통해 다운로드 가능 (가입 필요)

- Vivado,Vitis 설치(https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/vivado-design-tools.html)

- 정보 입력 후 다운로드

위 사항 체크 후 Next - 동의사항 체크

- 설치 위치 지정 후 설치

- amd.com - 다운로드 - FPGA 및 적응형 SoC에서 Vivado ML 개발자 툴을 통해 다운로드 가능 (가입 필요)

- 실습 사용 보드: Digilent사의 Cora Z7

Cora Z7: Zynq-7000 Single Core for ARM/FPGA SoC Development -

Support 탭에서 Reference Manual, Schematic 다운로드 가능

Cora Z7: Zynq-7000 Single Core for ARM/FPGA SoC Development

Shop now for USB test and measurement devices, FPGA development boards, programming solutions and educational products.

digilent.com

| 번호 | 명칭 | 번호 | 명칭 |

| 1 | Power select jumper (Ext. supply / USB) | 11 | 마이크로SD card 슬롯 (underside of board) |

| 2 | Power jack (for optional ext. supply) | 12 | USB 호스트 포트 |

| 3 | Shared USB JTAG / UART port | 13 | FPGA programming DONE LED |

| 4 | Unloaded expansion header | 14 | Processor subsystem reset button |

| 5 | Pmod connectors | 15 | 이더넷 포트 |

| 6 | SPI header (Arduino/ChipKIT compatible) | 16 | Power on reset button |

| 7 | Arduino/ChipKIT shield connectors | 17 | Power good LED |

| 8 | Programming mode jumper (JTAG / microSD) | 18 | Zynq-7000 |

| 9 | User tri-color LEDs | 19 | DDR3L 메모리 |

| 10 | User push buttons |

Designing with Verilog

- Verilog의 역사

- 1984년 - Gateway Design Automation에 의해 개발 / 회로 시뮬레이션 목적으로 사용

- 1995년 - IEEE(미국 전기전자 기술자 협회)에서 Verilog HDL의 국제 표준을 채택

- FPGA 및 ASIC 디자인에 적용

- System Verilog의 등장

- 현재 - Verilog와 SystemVerilog가 반도체 및 디지털 하드웨어 서례의 주요 언어로 사용

- Verilog의 특징

- 기본 구조

input a, b; output s, c; xor (a, b, s); and (a, b, c); - 모듈 단위 구성을 통해 input, output 제어

- 언어구조, 문법 등이 C언어와 유사

- 하드웨어 모델링&시뮬레이션을 위해 개발

- 대소문자 구분 - 키워드는 소문자로 사용

- 기본 구조

- Verilog 표준: Verilog-95 -> Verilog-2001 -> Verilog-2005 -> SystemVerilog(2017)

- Structural(구조적) Verilog vs. Behavior(동작적) Verilog

- Structural code of a half adder

- 디지털 회로의 물리적 구조 설명에 중점

- 대규모, 복잡한 설계에 적합

- Behavioral code of a half adder

input a, b; output s, c; always @ ( a or b ) begin s <= a + b; c <= a & b; end- 디지털 시스템의 동작 기술에 중점

- 논리 연산자 및 제어 흐름 구조(조건문, 반복문) 등을 통해 시스템의 동작 정의

- Structural code of a half adder

- Verilog의 추상화 수준(Levels of Abstraction)

- Verilog의 추상화: 디지털 회로 설계를 단순화하고 모델링하는 프로세스

- Behavioral Level(동작 수준)

- 가장 높은 추상화 수준, 디지털 시스템의 동작 기술

- 시스템의 기능적에 측면에 집중하며 하드웨어 구현에 대한 세부 정보 무시

- RTL(Register Transfer Level, 레지스터 전송 수준)

- 시스템의 동작을 레지스터 전송의 기본적인 연산 단위로 기술

- 레지스터, 레지스터 전송, 제어 신호 등을 사용하여 디지털 회로의 동작을 기술

- 대부분의 FPGA 및 ASIC 설계가 이루어지는 수준

- Gate level(게이트 수준)

- 논리 게이트 및 회로 요소(AND, OR, NOT 등)의 연결로 디지털 회로의 동작 설명

- 실제 하드웨어의 논리 게이트 레벨까지 내려가므로 매우 상세한 수준의 설계

- 전력소모, 시간적 제약 등 하드웨어 구현의 물리적인 측면 고려에 사용

- 계층적 설계(Hierarchical design):디지털 시스템을 작은 모듈로 나누어 각각을 독립적으로 설계하고 구현하는 방법

- 모듈화

- 시스템을 작은 모듈로 나누어 각 모듈을 개별적으로 설계 & 구현

- 각 모듈은 특정 기능을 수행하며 상위 수준 모듈은 하위 수준 모듈을 조합하여 시스템 동작 정의

- 계층적 구조

- 상위 수준 모듈이 하위 수준 모듈 포함

- 계층 구조를 통해 시스템의 복잡성을 단순화하고 모듈 간의 상호작용 관리

- 유지 보수

- 각 모듈은 독립적으로 테스트&디버깅이 가능하며 수정 및 업데이트가 가능

- 시스템의 특정 부분을 수정할 때 다른 부분에 영향을 미치지 않아 유지 보수에 용이

- 모듈화

Verilog의 키워드&식별자

- 키워드(Keywords): 언어 구조를 위해 약속된 식별자 / 반드시 소문자로 작성해야 함

- example) module, endmodule, input, output

- 식별자(Identifiers): 사용자가 붙이는 이름

- 반드시 알파벳이나 언더바로 시작해야함

- example) full_add, a, b, c_in, c_out

- 주석: C언어와 동일하게 //, /*~*/를 사용

- 단일행 주석: // 주석내용 입력

- 여러 행 주석: /* ~~여러 줄에 걸쳐 주석 입력 */

Vivado 실습

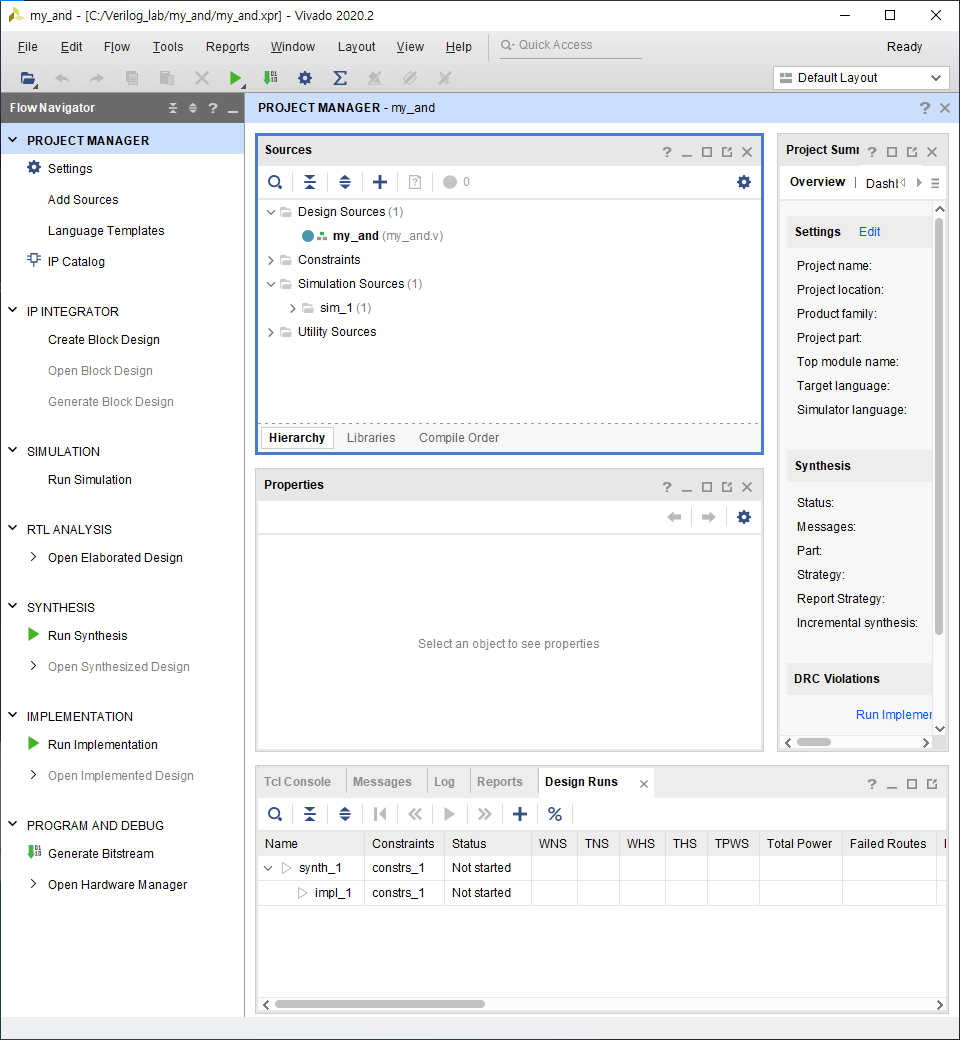

1. Quick Start - Create Project - Next - 프로젝트 이름(my_and), 위치(C:/Verilog_lab) 설정

*이름, 위치는 반드시 영문으로 공백, 특수문자('_' 제외), 한글 없이 작성

2. RTL Project - Next

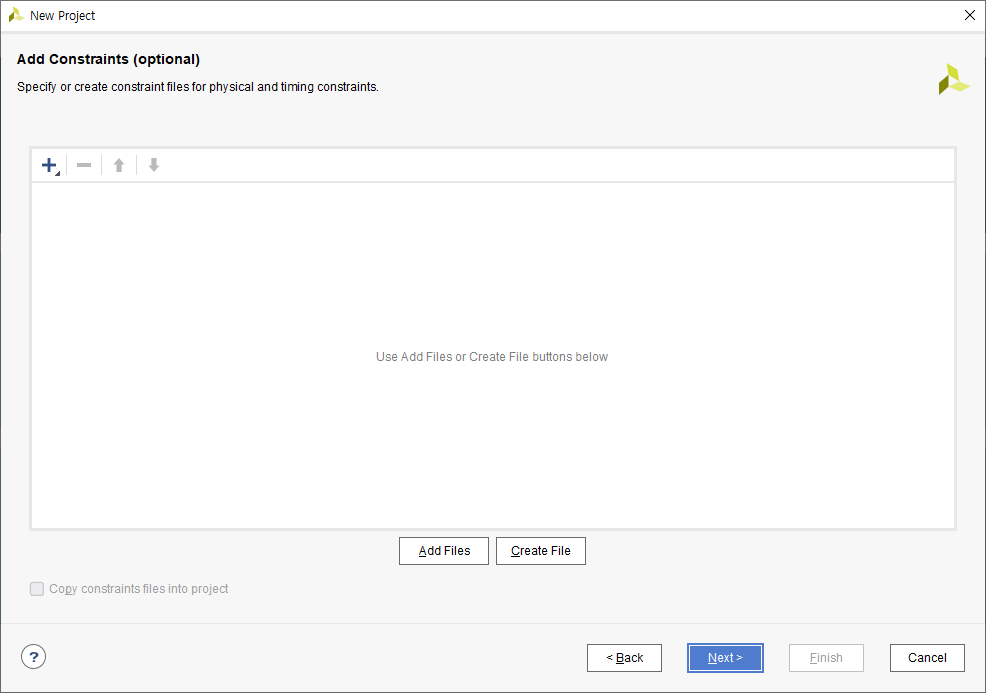

3. Next

4. Next

5. [Device 선택 화면]

6. 최종 Summary 확인 - Finish

7. 실행 화면

8. Add Sources - Add or create design sources

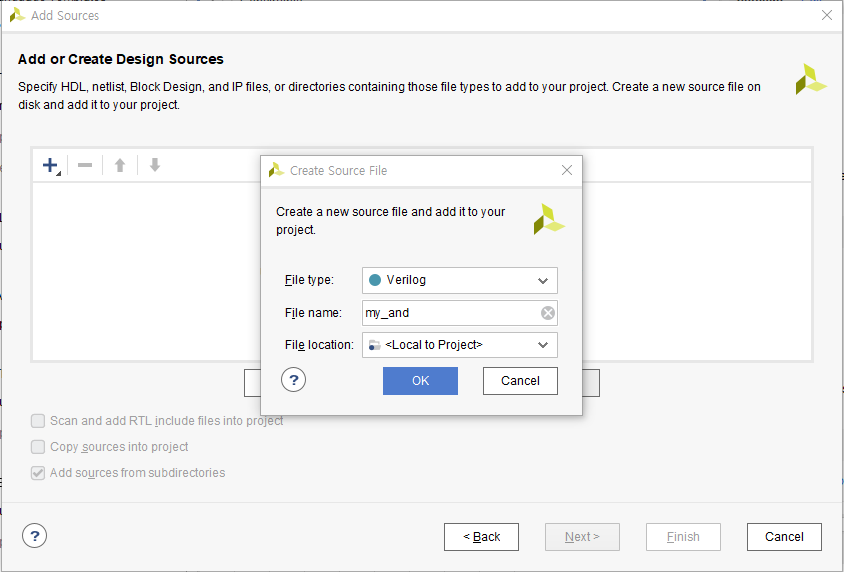

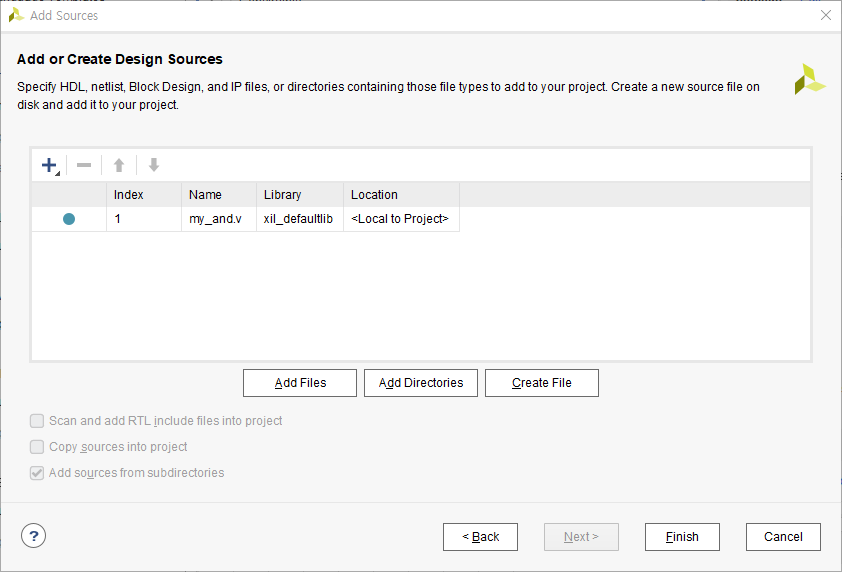

9. Next - Create File - type(Verilog), name(my_and) 입력 - OK - Finish

10. Define Module창에서 Port Name과 Input/Output 설정 - OK

11. Sources - Design Sources에 my_and.v 형성 확인, open

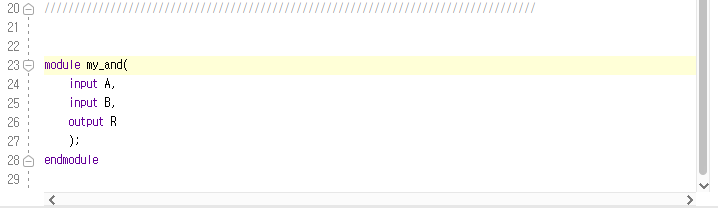

12. my_and.v 파일을 열어 다음 코드 확인

13. [Code Example]

R = A AND B 만들 때:assign R = A&B; (assign은 키워드, 소문자로 입력) / assign 의미: 새로운 신호 생성

14. Ctrl+S(저장) 후 Message 탭을 통해 오류 확인

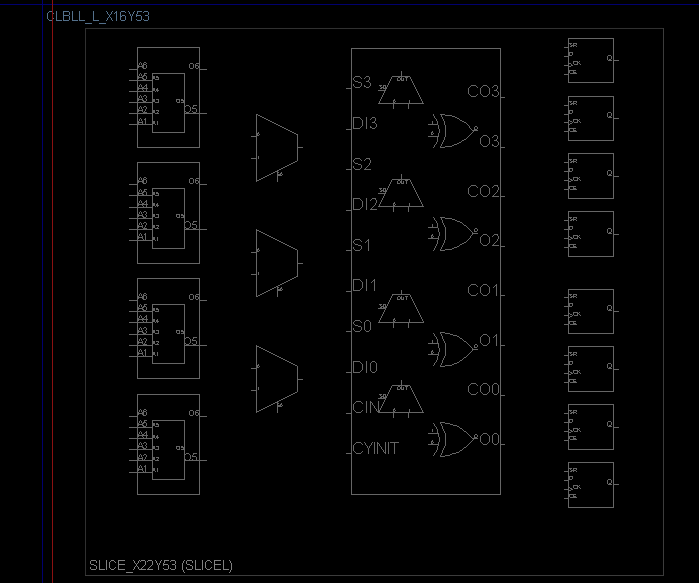

15. Flow Navigator- RTL Analysis - Open Elaborated Design을 통해 게이트 확인

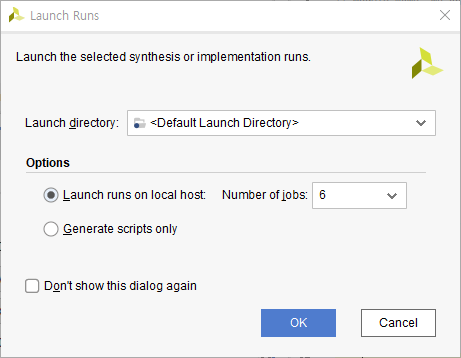

16. Run Synthesis

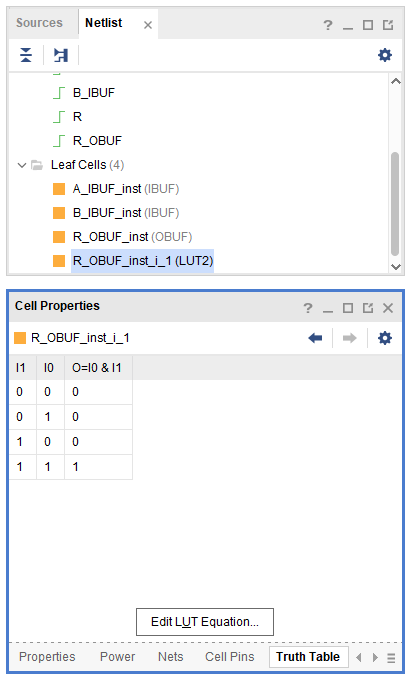

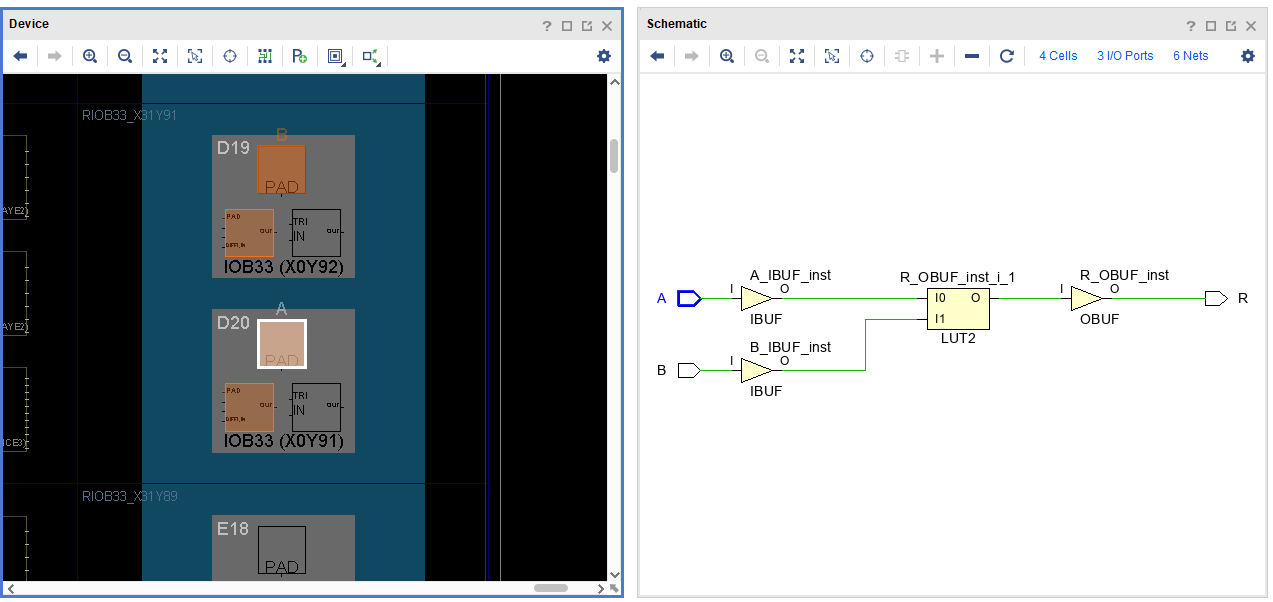

17. Schematic 구조 확인

18. 진리표 확인

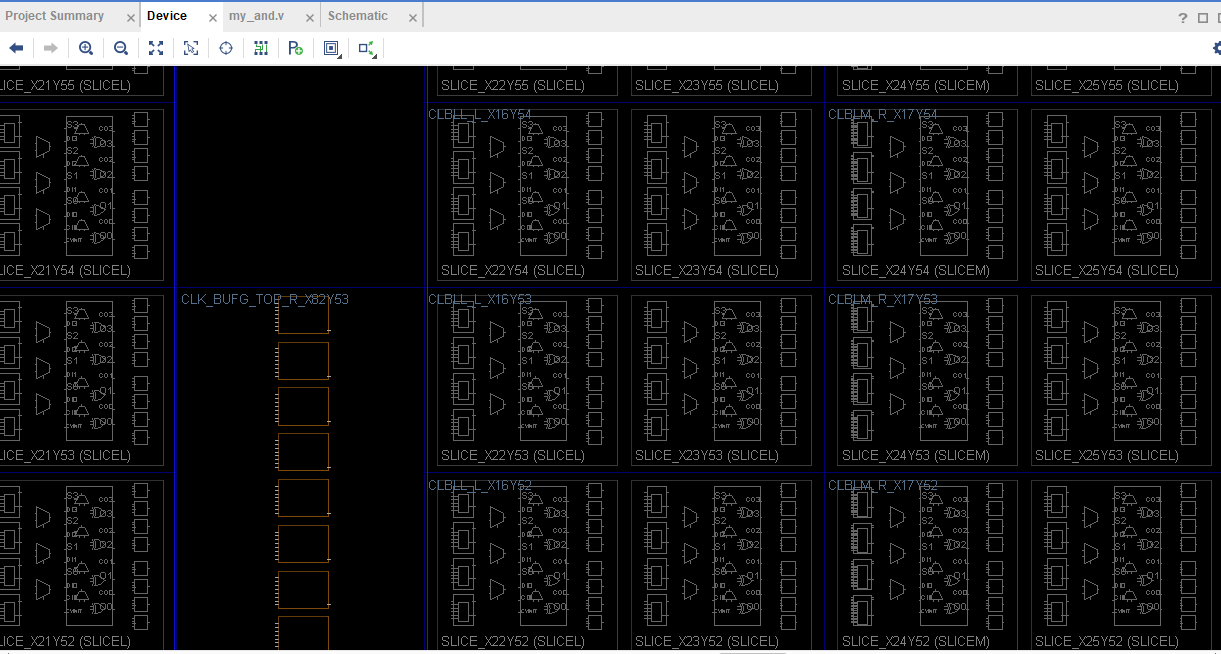

19. Device 탭에서 좌클릭-드래그 시 확대 가능

20. 우측 상단 Default Layout -> I/O Planning

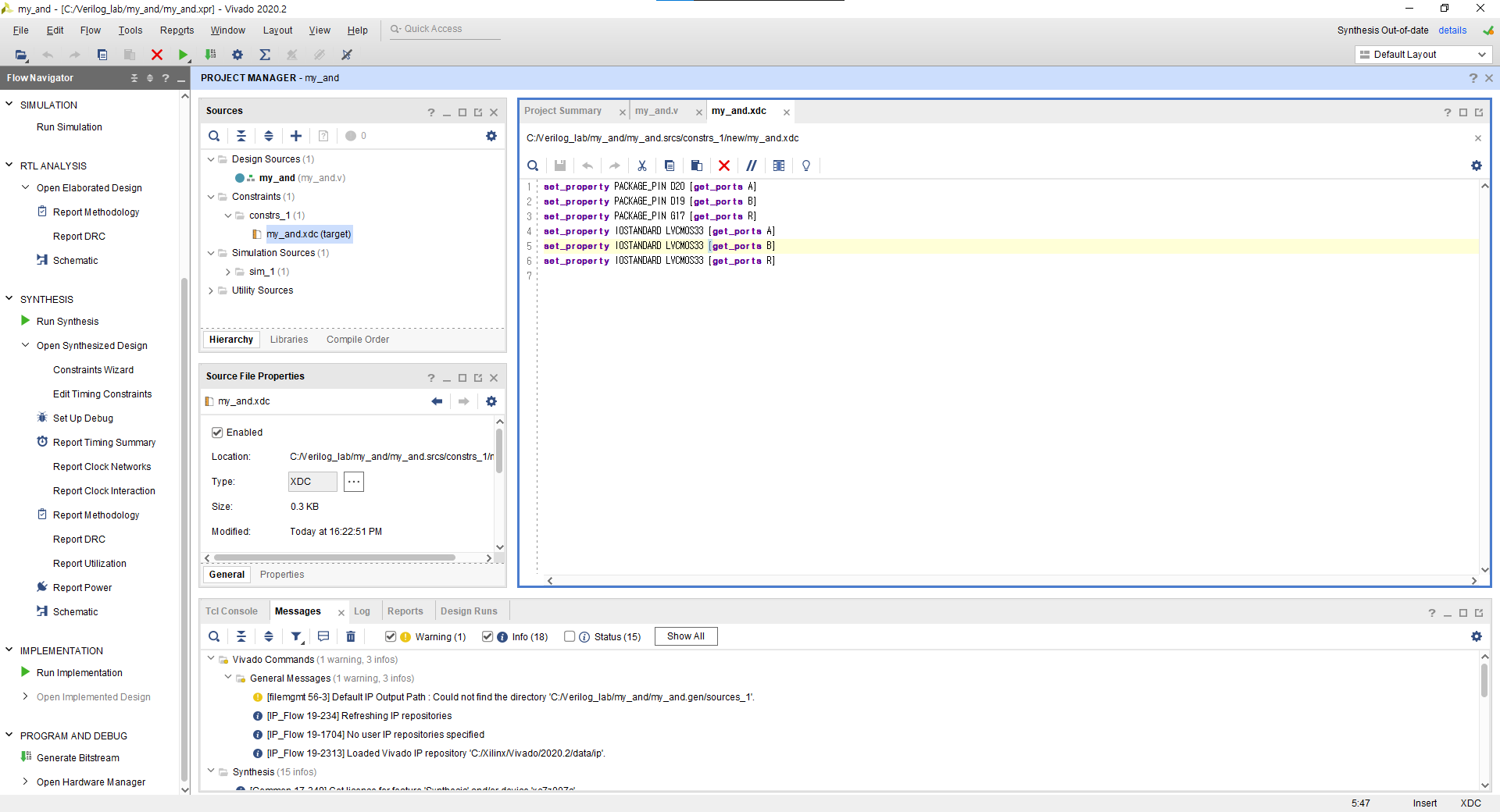

- 하단의 Package Pin: Pin 번호를 schematic을 참조하여 A는 BTN0, B는 BTN1, R은 LEDO_G -> 입력

Schematic

21. LVCMOS 12 -> 1.2V, LVCMOS 15 -> 1.5V ... LVCMOS33으로 모두 설정

22. 우측 상단의 파란색 창의 X를 눌러 종료

23. 종료 후 Sources의 Constraints에 파일 생성 확인

24. 해당 파일을 열어 올바른 핀에 할당되었는지 확인(아래 창에서 핀 번호 수정 가능)

25. Navigator - Run Implemntation 클릭

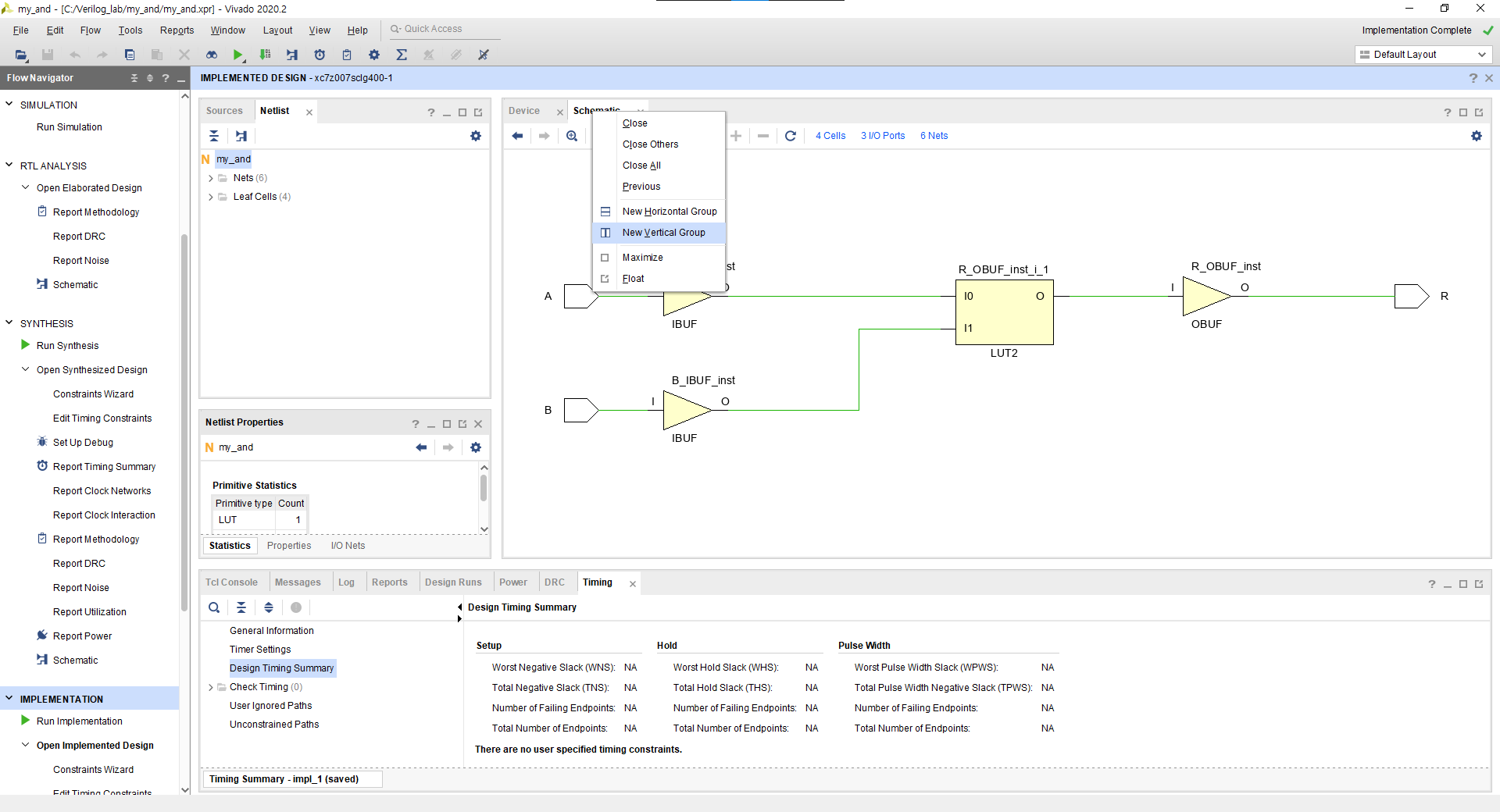

26. 실행 후 Netlist의 my_and 우클릭-Schematic

27. Schematic 윈도우 탭 우클릭 - New Vertical Group

28. Schematic 창에서 라인 선택하면 화살표 생성

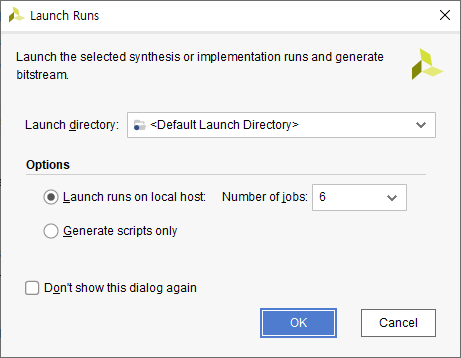

29. Navigator - Generate Bitsream - OK

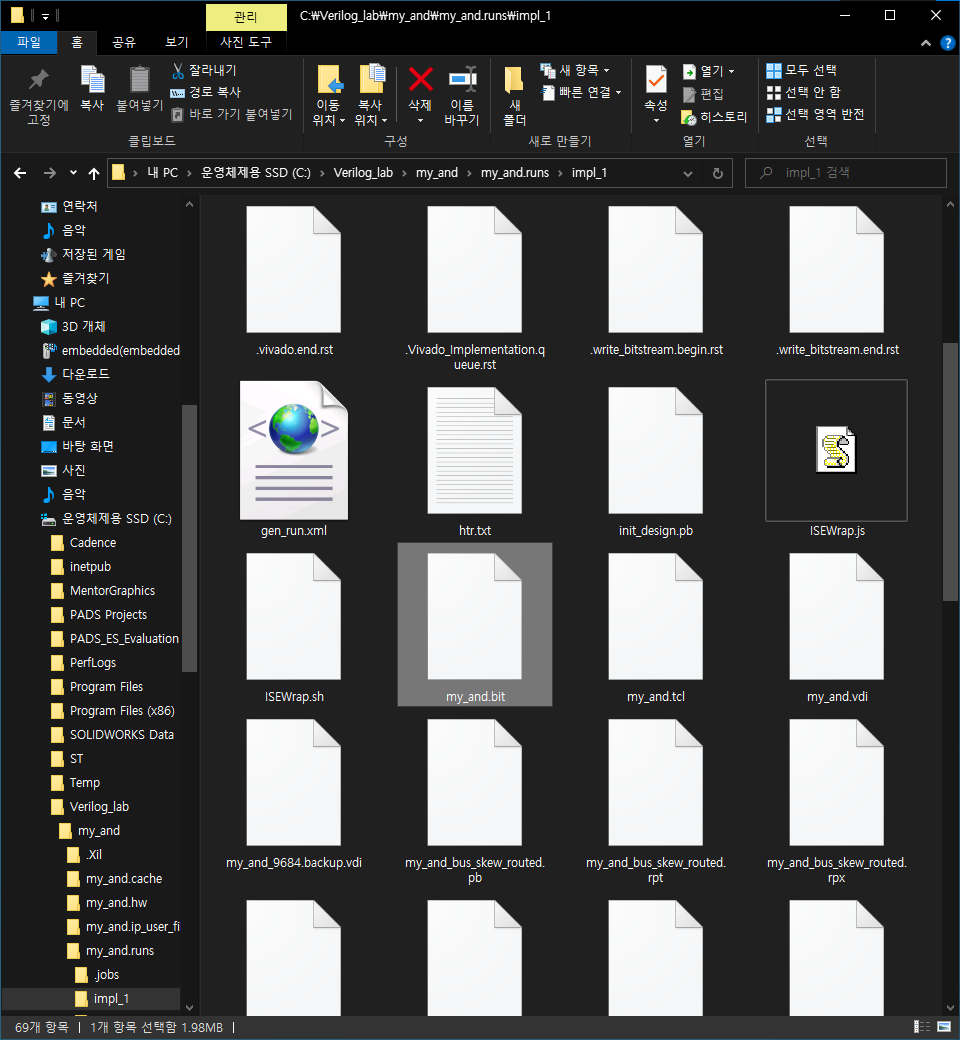

30. 종료 후 프로젝트 명 폴더(my_and)에 my_and.runs, my_and.srcs확인

31. C:\Verilog_lab\my_and\my_and.runs\impl_1에 my_and.bit 확인