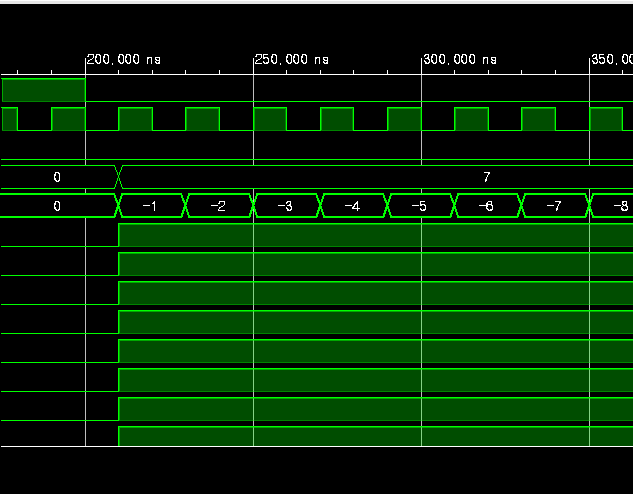

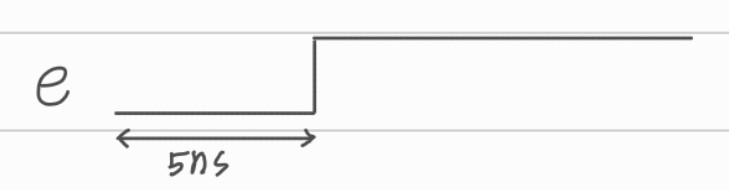

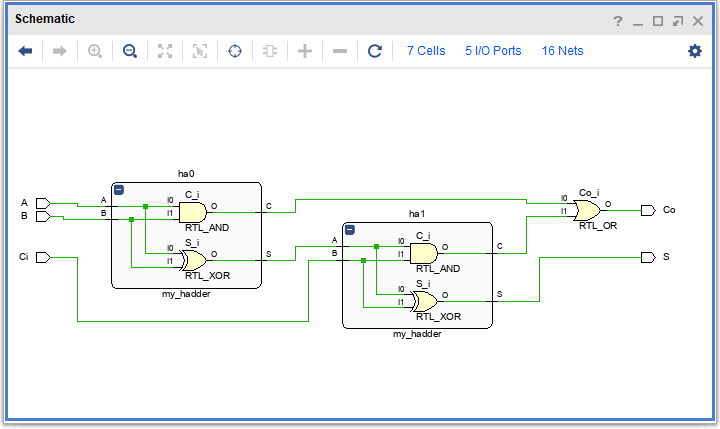

[2024.04.01.월] 인천인력개발원 하만 세미콘 아카데미 Verilog를 이용한 RTL 시스템 반도체 설계 Clock과 Reset Clock(clk, 클록) 디지털 시스템에서 데이터 처리의 타이밍을 제어하는 주기적인 신호 주파수, 주기를 통해 신호의 반복속도, 시간 등을 나타냄 Reset(rst) 디지털 시스템을 초기 상태로 되돌리는 데 사용 Synchronous Reset: 클록 신호에 동기화되어 작동 - 리셋 시 다음 클록 엣지에서 시스템 초기화 Asynchronous Reset: 클록 신호와 무관하게 즉시 작동 - 빠른 리셋이 가능하지만 동기화 문제 발생 가능 Flip-Flop(FF) 한 비트의 이진 정보를 저장하는 메모리 단위 클록 신호에 의해 제어 입력 데이터를 기반으로 두 가지 안정된 상..