1. New Project 생성 - Source 추가: 전 과정에서 생성된 myip2_slave_lite_v1_0_S00_AXI.v 파일, segment 출력 파일

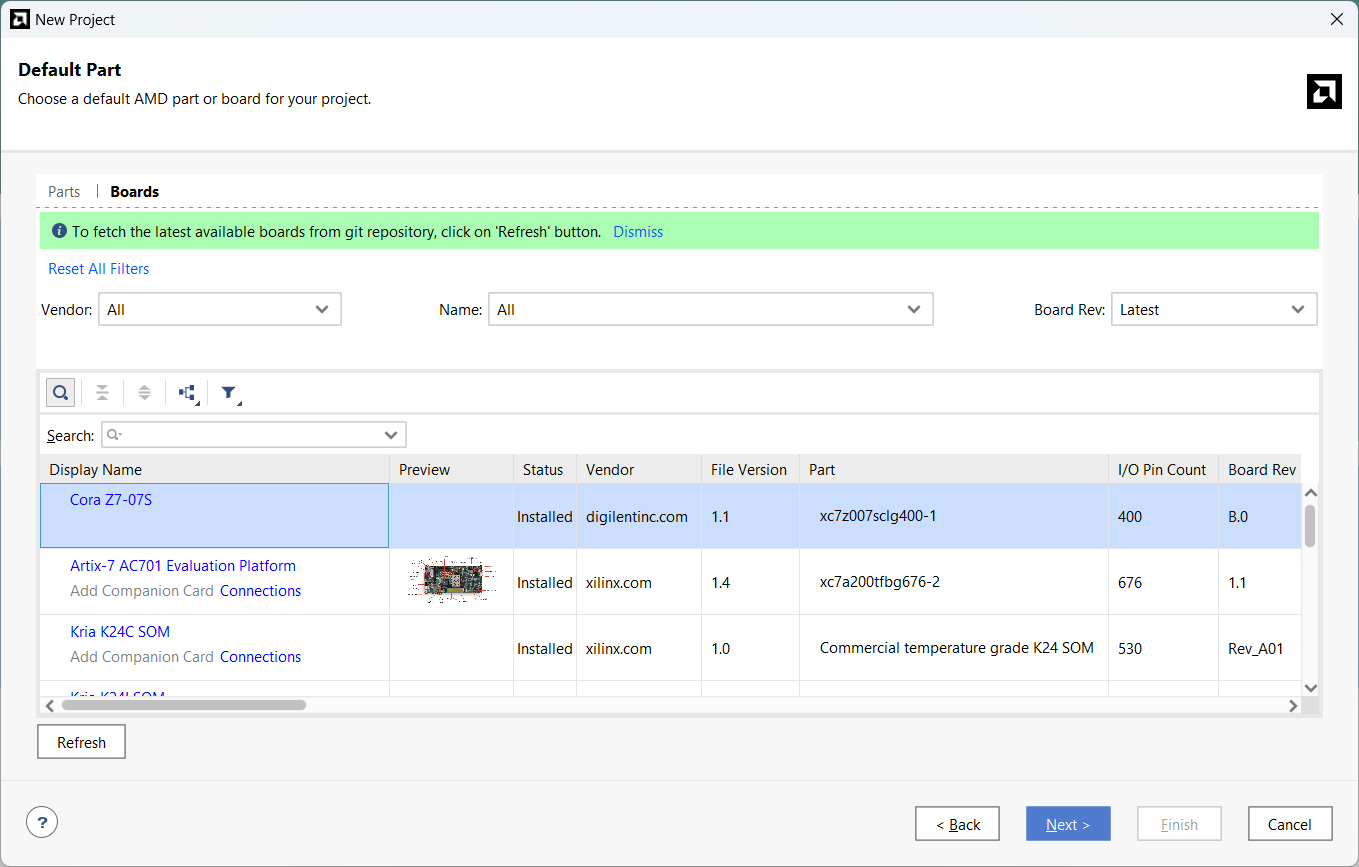

2. 보드 선택 후 finish

3. myip2_slave~~.v에서 segment와 연결하기 위한 hi_bit과 low_bit을 output으로 선언

4. myip2_slave~~.v에서 output으로 나갈 high bit와 low bit에 slave의 register 값을 나누어 할당

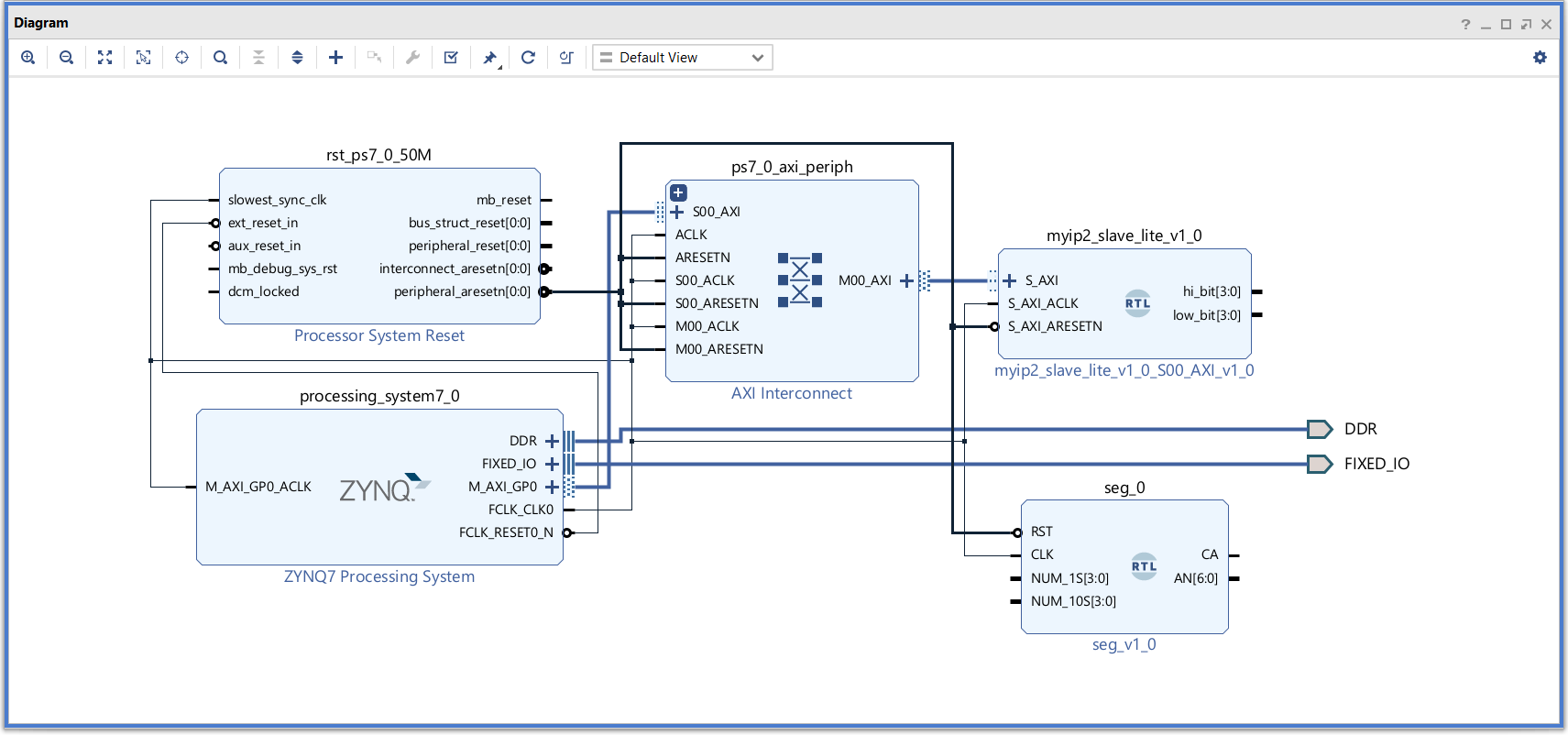

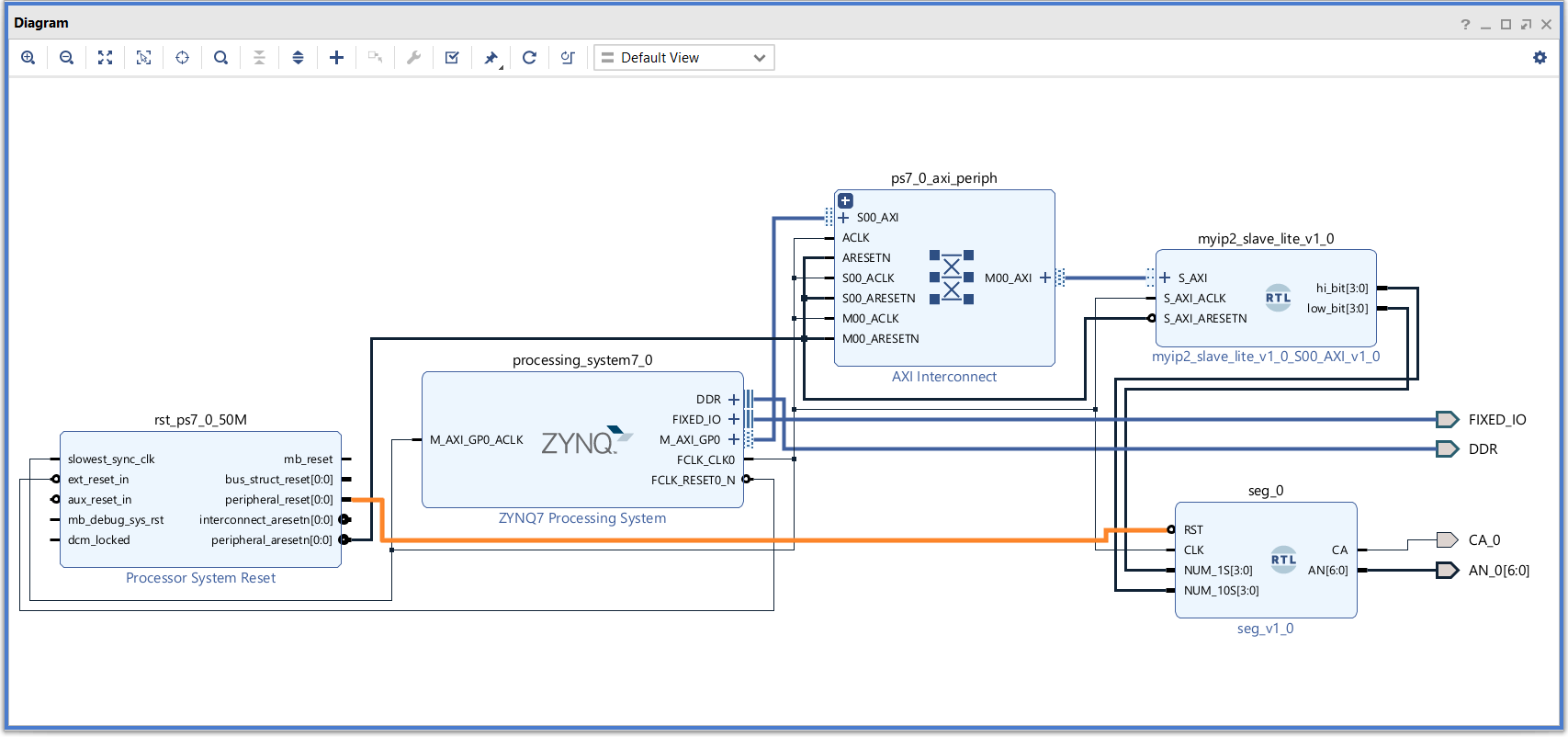

5. Create Block Desgin - Zynq 추가 - Run Block Automation

6. Zynq7의 Ethernet, USB 포트 비활성화

7. PS/PL Interface 확인

8. Add module - 모듈 추가

9. Run Connectino Automation

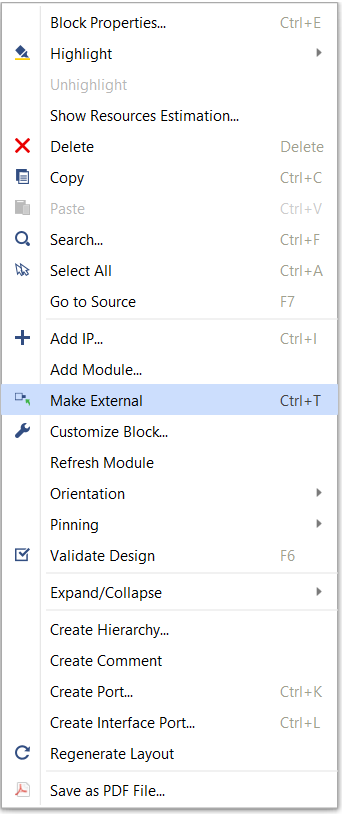

10. Make External

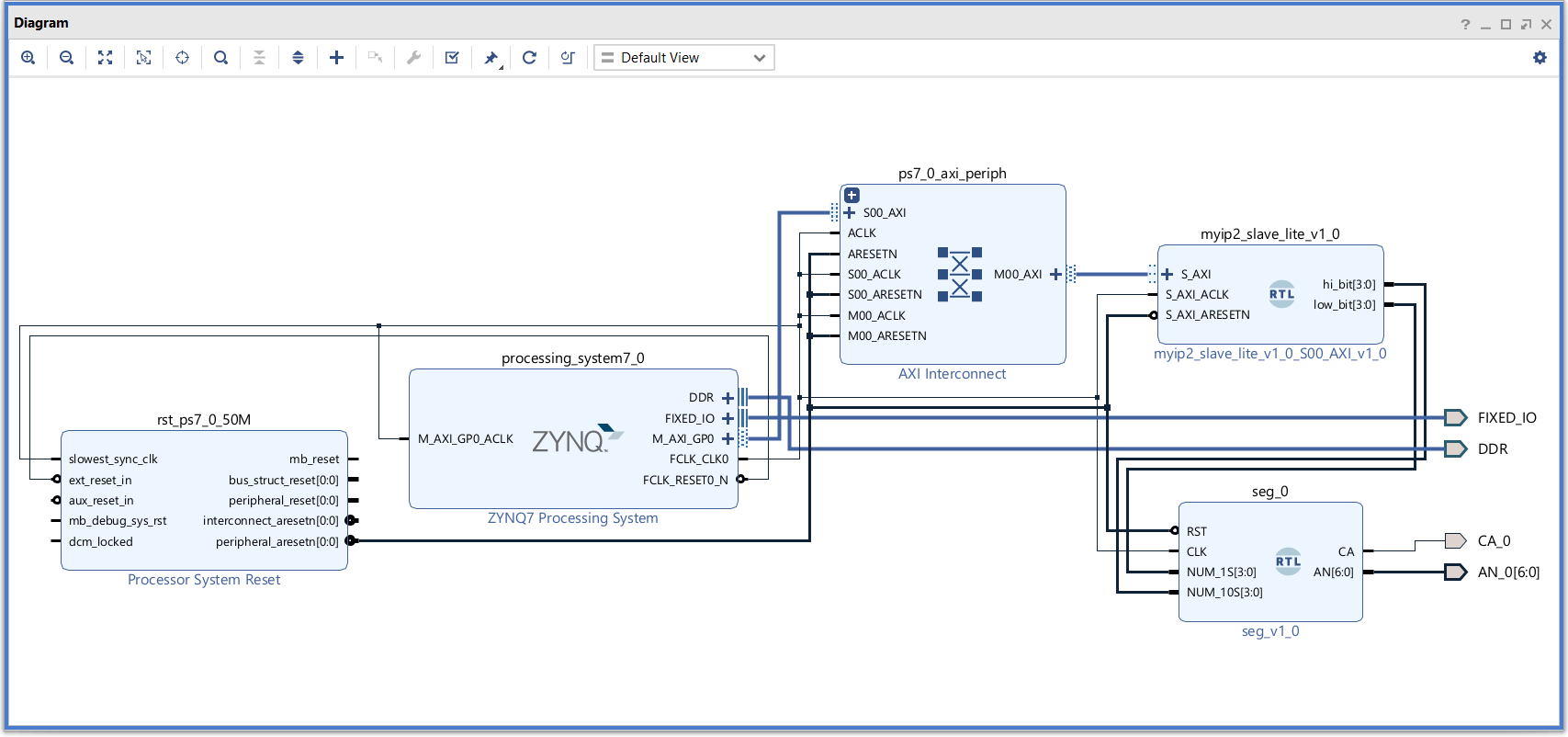

11. seg_0의 RST를 rst_ps7_0_50M의 peripeheral_reset에 연결

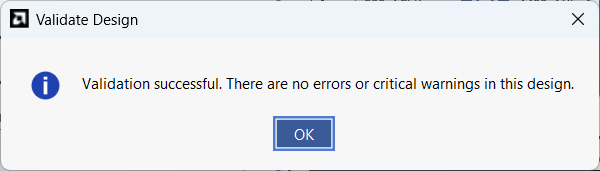

12. Validate Desgin으로 체크

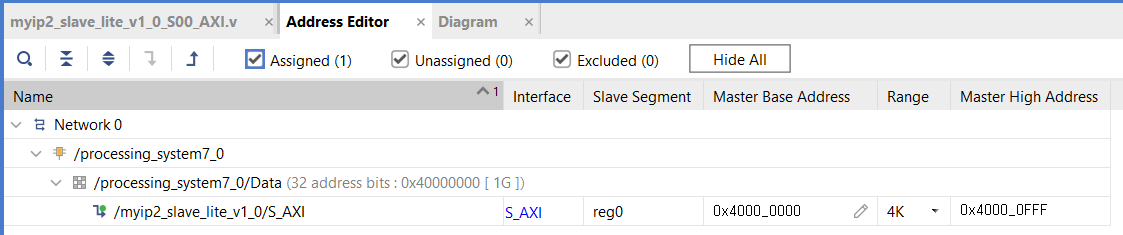

13. Register의 Address 확인

14. Block Design 종료 후 axi_seg.bd에 대해 Create HDL Wrapper

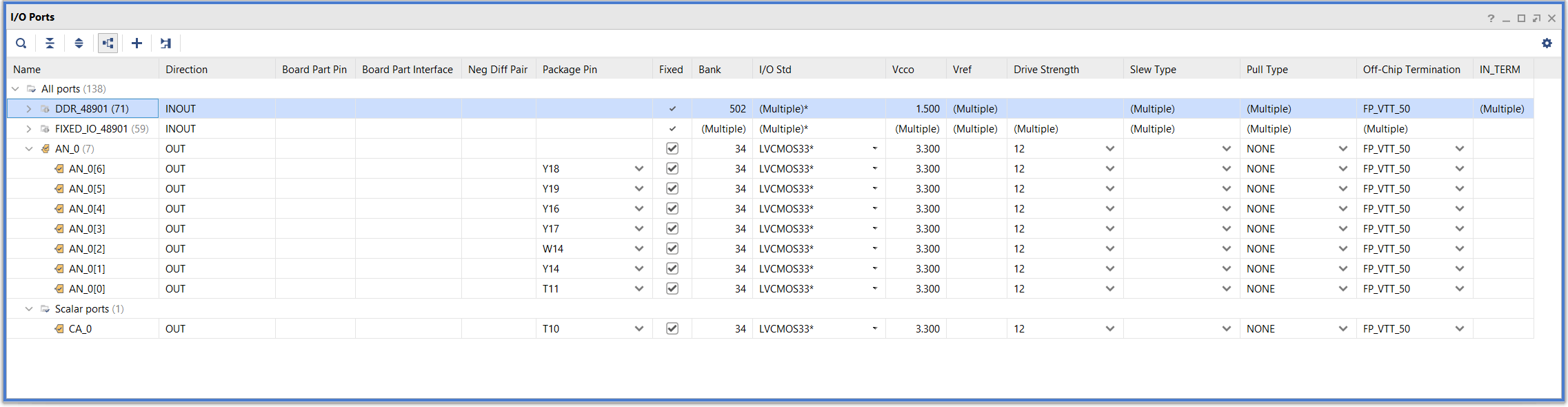

15. Run Synthesis - Open Synthesized Design - CA, AN 핀 할당

16. Constraint 파일 저장 및 Generate Bitstream

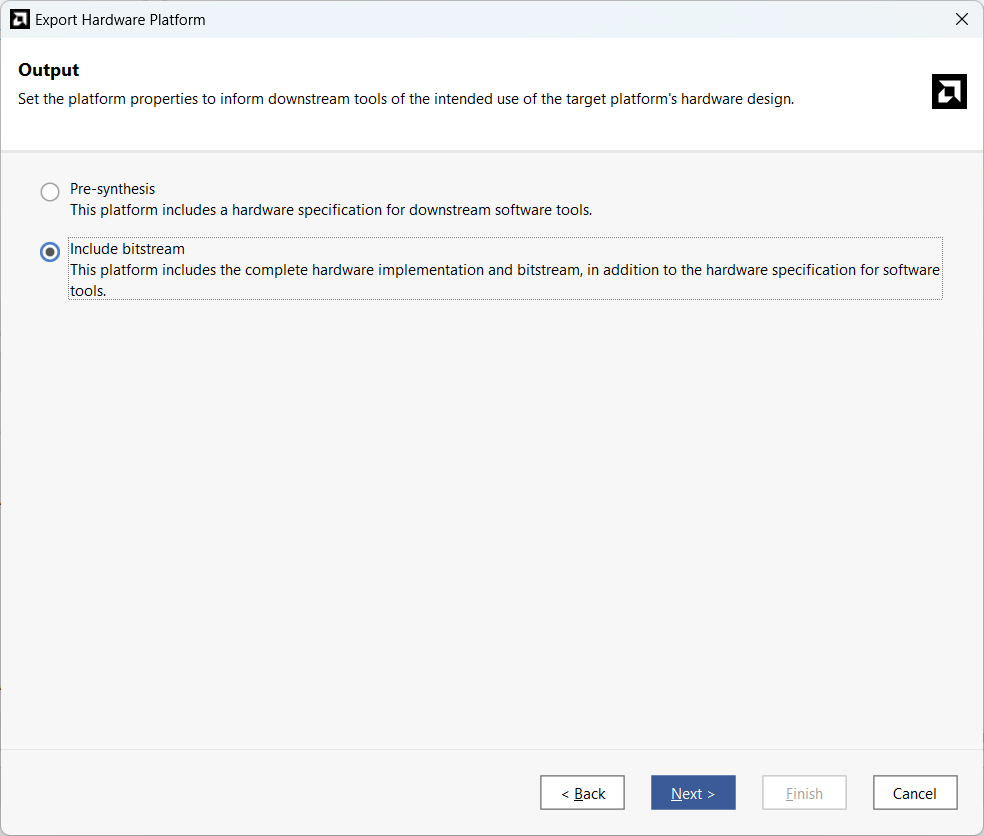

17. File - Export - Export Hardware - Include Bitstream

18. Vivado 종료 후 Vitis 실행

19. Open Workspace로 my_axi_seg 열기

20. Create Platform Component - 위에서 생성한 xsa 파일 선택

21. Create Application Component - From Example - Empty Application으로 생성

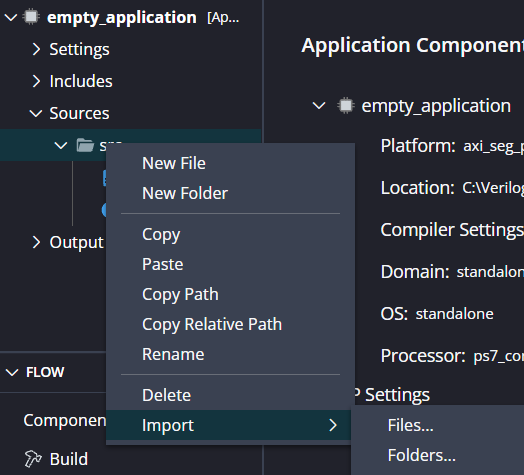

22. source -> src에서 import file, 위에서 사용한 my_axi_test2.c 파일 추가 후 test.c로 이름 수정

'하만(Harman) 세미콘 반도체 설계 과정 > SoC를 위한 Peripheral 설계' 카테고리의 다른 글

| AMBA AXI (0) | 2024.07.15 |

|---|---|

| AXI 프로토콜 / HandShake (0) | 2024.06.26 |

| 하만(Harman) 세미콘 아카데미 71일차~ - SoC를 위한 Peripheral 설계(CPU, SoC, AMBA Bus, HandShake, AXI 프로토콜) (1) | 2024.06.25 |