STRAIT(1) _ AI 가속기의 자가 테스트 및 복구 기술

이번 포스팅은『STRAIT: Self-Test and Self-Recovery Architecture for Systolic-Array-Based AI Accelerators』 논문을 바탕으로 제작되었습니다. 최근 AI 가속기의 신뢰성과 안전성이 중요해지면서, Systolic Array 기반 AI

semicon-circuit.tistory.com

지난 포스팅에서 STRAIT의 개념, 구조를 살펴보았습니다. 이번 포스팅에서는 세부적으로 자가 테스트 과정을 살펴봅니다.

Test Process With Scan Chain

자가 테스트는 Scan Chain을 활용하여 이루어집니다. 여기서 Scan Chain이란, 내부 레지스터를 직렬로 연결하여 결함 테스트 패턴을 주입하고 결과를 수집하는 구조입니다.

Scan Chain에 대한 간략한 원리는 아래 게시글에 포스팅되어 있습니다.

하만(Harman) 세미콘 아카데미 58-62일차 - Full Custom IC One Chip 설계(Scan Chain 설계, Amplifier, One Chip 설계

Team Project - Scan ChainScan Chain이란?디지털 회로 내부에서 테스트를 용이하게 하기 위해 Flip Flop을 직렬 연결하여 내부 상태를 쉽게 접근, 제어할 수 있도록 하는 회로Flip Flop에 21MUX를 연결하여 테스

semicon-circuit.tistory.com

STRAIT 구조에서 Scan Chain은 PE간의 연결을 재활용하여 구성되며, 이로 인해 하드웨어 오버헤드를 최소화할 수 있습니다.

STRAIT의 Scan Chain의 구성은 다음과 같습니다.

- Activation Registers: 동일한 행(Row)의 레지스터들을 수평으로 연결합니다.

- Weight Registers: 동일한 열(Column)의 레지스터들을 수직으로 연결합니다.

- Partial Sum Registers: 동일한 열(Column)의 레지스터들을 수직으로 연결하며, STRAIT에서 스캔 데이터 전달을 위한 주요 경로로 사용됩니다.

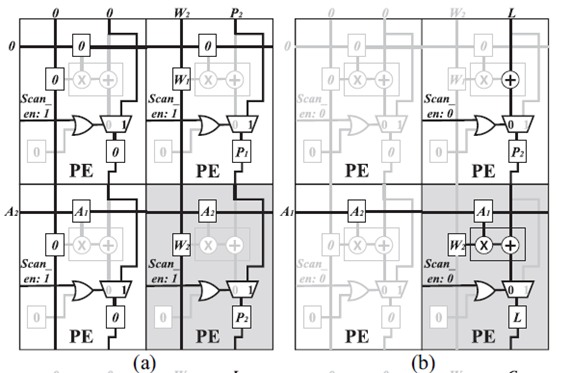

Partial Sum Registers을 이용한 스캔 데이터 전달 시에는 scan_en 신호를 사용하며, 각 PE에 MUX가 추가되어 scan_en 신호가 HIGH 일 때 테스트 데이터 이동 경로가 생성됩니다.

Stuck-At(SA) Test Process

SA 테스트는 각 회로 노드에 대해 0 또는 1이 고정되어 있는 결함(Stuck-at-0, Stuck-at-1)을 검출하기 위한 전통적인 테스트 기법입니다. STRAIT에서는 아래와 같은 과정으로 SA 테스트를 수행합니다.

1. 테스트 데이터 삽입 (Scan Shift)

- scan_en = 1로 설정되면 각 열의 스캔 체인에 테스트 패턴(S1, S2, S3)을 삽입

- 모든 PE에 동일한 테스트 데이터가 입력됨

- 스캔 체인 경로를 따라 아래쪽 PE까지 데이터 이동

2. 캡처(Capture) 단계

- 테스트 데이터가 모두 삽입되면, scan_en = 0으로 설정

- 각 PE 내부의 Functional Path를 통해 연산 수행

- 연산 결과가 Partial Sum Register에 저장됨

3. 결과 분석

- 다음 테스트 데이터가 삽입될 때, 이전 캡처 결과(C)가 출력

- 출력된 Partial Sum 값(C)을 비교하여 결함 유무 판단

- Activation / Weight 값을 따로 읽을 필요 없이, 그 영향을 반영한 결과만으로 분석 가능

- 모든 PE가 동일한 입력을 받아 결과 비교가 간단 (예상값이 고정됨)

Stuck-At Test Process는 다음과 같은 특징을 나타냅니다.

- 모든 PE는 동일한 테스트 데이터로 테스트를 진행하므로, Shift Power가 절약됩니다.

- Partial Sum Register를 스캔 체인으로 활용하므로 불필요한 스캔을 생략할 수 있습니다.

Transition-Delay(TD) Test Process

TD 테스트는 회로 노드에서의 전압 변화(0→1 또는 1→0 전이)가 제한 시간 내에 완료되지 못하는 결함을 검출하기 위한 테스트 기법으로, 실제 동작 속도에서의 전이(0→1 또는 1→0)를 감지함으로써 타이밍 결함 여부를 판단할 수 있습니다. STRAIT에서는 아래와 같은 과정으로 TD 테스트를 수행합니다.

1. 테스트 데이터 삽입 (Scan Shift)

- scan_en = 1로 설정되면, 선택된 PE의 스캔 체인을 통해 테스트 데이터가 삽입됨

- 나머지 PE의 스캔 체인에는 0이 삽입되어 토글(Toggle) 수를 최소화

- 삽입된 값은 런치(Launch) 직전 Functional Path를 통해 저장됨

2. 런치 사이클 (1st Capture Cycle)

- scan_en = 0으로 설정 후, at-speed 클럭을 통해 전이 발생

- 예: 상위 PE의 활성화 값(A1)과 부분합(P2)이 런치되어 대상 PE에 입력됨

- 입력된 값은 실제 동작 경로(Functional Path)를 통해 전달

3. 전이 데이터 전파

- Functional Clock이 인가되면, PE 내부 연산 결과가 다음 단계의 레지스터로 전파됨

- 이 과정을 통해 지연이 발생했는지 여부를 실제로 확인 가능

4. 캡처 사이클 (2nd Capture Cycle)

- 두 번째 클럭(2nd cycle)에서 연산 결과를 캡처

- 전이 전파가 실패했을 경우, 오류가 발생한 부분이 캡처된 값에 반영됨

5. 결과 분석

- 캡처된 결과(C)는 다음 테스트 주기에서 출력

- 출력 데이터를 예상값과 비교하여 전이 결함(Transition Fault) 유무 판단

- 분석 방식은 SA 테스트와 유사하며, 비교가 간단함

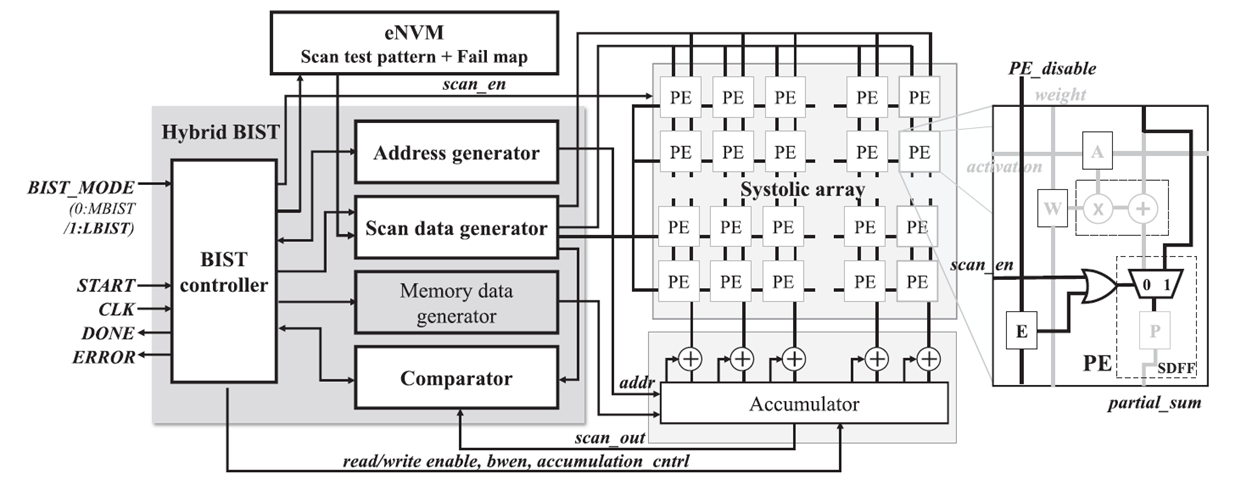

MBIST(Memory BIST)

MBIST는 Systolic Array 내부의 Weight, Activation, Partial Sum과 같은 메모리 블록을 자동으로 테스트하는 구조입니다.

MBIST 구성 요소는 다음과 같습니다.

- MBIST Controller: 테스트 전체를 제어하는 중앙 제어기

- Address Generator: 테스트할 대상 메모리의 주소 생성

- Data Generator: Write/Read 테스트용 데이터 생성

- Comparator: 메모리로부터 읽은 데이터와 기대값 비교

MBIST의 Test Process는 다음과 같습니다.

- MBIST Controller가 내장된 알고리즘 또는 사용자 정의 알고리즘에 따라 테스트 제어 신호를 생성합니다.

- Address Generator가 테스트 대상 메모리의 주소를 생성합니다.

- Data Generator가 테스트용 write/read 데이터를 생성합니다.

- 생성된 주소 및 데이터 신호가 메모리와 Comparator로 전송합니다.

- 메모리에서 읽은 데이터와 예상 값이 Comparator에서 비교됩니다.

- 비교 결과가 MBIST Controller로 전달되어 최종 합/불을 판정합니다.

[LBIST(Logic BIST)

LBIST는 Systolic Array 내부의 MAC 유닛, 제어 로직 등의 연산 로직을 자동으로 테스트하는 구조입니다.

LBIST 구성 요소는 다음과 같습니다.

- LBIST Controller: LBIST 하위 모듈을 제어하고 스캔 절차에 따라 Systolic Array와 누산기 블록 구동

- Address Generator: 누산기 블록의 내부 메모리 유닛에 스캔 출력 데이터 읽기/쓰기 메모리 주소 적용

- Scan Data Generator: 스캔 입력 데이터와 예상 스캔 출력 데이터를 스캔 입력과 비교기에 각각 제공

- Comparator: 스캔 출력 데이터를 예상 스캔 출력 데이터와 비교

- eNVM: Systolic Array 테스트 패턴을 저장

LBIST의 Test Process는 다음과 같습니다.

- LBIST Controller가 내부 하위 모듈을 제어하고 스캔 테스트 절차를 시작합니다.

- Scan Data Generator는 테스트용 scan-in 데이터를 생성합니다.

- 생성된 데이터는 Systolic Array 내 PE들의 스캔 체인으로 삽입됩니다.

- 스캔 종료 후, Systolic Array의 scan-out 데이터는 Accumulator 블록의 메모리에 저장됩니다. 이때 저장 주소는 Address Generator가 지정합니다.

- Comparator가 저장된 scan-out 데이터와 기대값을 비교합니다.

- 비교 결과에 따라 LBIST Controller는 해당 PE의 테스트 통과 여부를 판정합니다.

Hybrid BIST: MBIST + LBIST

STRAIT에서는 Systolic Array와 같은 대규모 연산 구조의 결함을 효과적으로 검출하기 위해, 전통적인 스캔 기반 테스트 대신 Hybrid BIST(Built-In Self-Test) 구조를 사용합니다.

Hybrid BIST는 MBIST(Memory BIST)와 LBIST(Logic BIST)의 기능을 통합한 구조로, 연산 유닛 내에 내장된 구조만으로 테스트 데이터를 생성하고, 결과를 비교하여 결함 유무를 판단할 수 있습니다. 이를 통해 외부 테스트 장비 없이도 내부 회로의 정합성과 신뢰성을 검증할 수 있으며, 테스트에 필요한 핀 수와 테스트 시간, 전력 소모를 획기적으로 줄일 수 있습니다.

또한, MBIST와 LBIST 두 테스트 방식이 유사한 하드웨어 구조를 가지기 때문에 대부분의 모듈을 공유할 수 있습니다.

STRAIT에서 전체 테스트 동작 순서는 아래와 같습니다.

- BIST Logic Test (Hybrid BIST 자체 검증)

- 하이브리드 BIST 내부 로직이 동작 가능한지 먼저 스캔 테스트로 점검 → 불합격 시 칩 폐기

- Memory Test (MBIST 모드)

- Accumulator 내부 메모리 테스트 수행

→ Pass: 다음 단계 진행

→ Fail: 수리 가능한 경우 복구, 불가능하면 칩 폐기

- Accumulator 내부 메모리 테스트 수행

- Systolic Array Test (LBIST 모드)

- 스캔 체인부터 시작하여 전체 Systolic Array의 로직 테스트 수행

→ Pass: 최종 테스트 성공

→ Fail: 수리 가능 시 복구, 불가능 시 칩 폐기

- 스캔 체인부터 시작하여 전체 Systolic Array의 로직 테스트 수행

- Test Pass or Fail

- 모든 테스트 통과 시 Test Pass

- 중간 단계에서 복구 불가 판정 시 Test Fail

다음 포스팅: STRAIT의 Self-Diagnosis

STRAIT(3) _ Self-Diagnosis

STRAIT(2) _ BIST(Built-In Self Test)STRAIT(1) _ AI 가속기의 자가 테스트 및 복구 기술이번 포스팅은『STRAIT: Self-Test and Self-Recovery Architecture for Systolic-Array-Based AI Accelerators』 논문을 바탕으로 제작되었습니

semicon-circuit.tistory.com

'반도체 시사' 카테고리의 다른 글

| STRAIT(4) _ BISR(Built-In Self-Recovery) (0) | 2025.05.06 |

|---|---|

| STRAIT(3) _ Self-Diagnosis (0) | 2025.05.06 |

| STRAIT(1) _ AI 가속기의 자가 테스트 및 복구 기술 (2) | 2025.05.05 |

| AI 가속기(5) _ Systolic Array 설계의 도전 과제 (1) | 2025.05.05 |