UART란?

- UART(Universal Asynchronous Receiver/Transmitter, 범용 비동기화 송수신기)는 데이터 버스로부터 병렬로 받은 데이터를 직렬 방식으로 전환하여 다른 UART로 전송하는 컴퓨터 하드웨어의 한 종류이다.

- UART로부터 직렬 데이터를 수신한 다른 UART는 이를 병렬 방식으로 전환하여 데이터 버스에 전송한다.

- 통신에 사용되는 데이터는 메모리나 레지스터에 저장되어 있으며, 이를 차례데로 읽어 직렬로 통신한다. 기본 단위는 최대 8비트이다.

UART 통신의 특징

- UART는 비동기식(Asynchronous) 통신 방식으로 RX와 TX 각각의 clock 신호를 사용한다.

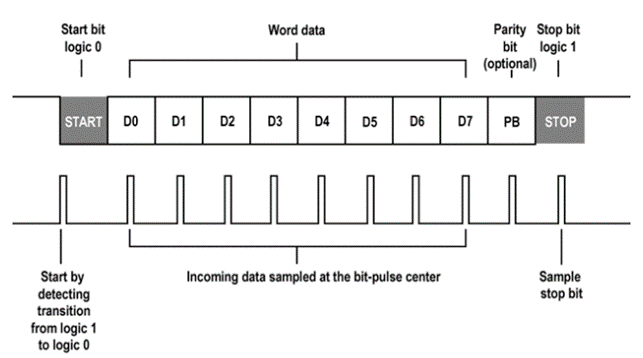

- Bit 구성

- Start Bit: 전송 데이터 패킷의 시작 부분을 알린다. 이 신호를 통해 RX에서 데이터 수신을 시작한다

- Data Bits: Start Bit와 Stop Bit 사이에 존재한다. 최대 9bit까지 데이터 통신이 가능하다.

- Parity Bit: 선택적으로 사용 가능한 Bit로, 대표적으로 Odd Parity(홀수 패리티)와 Even Parity(짝수 패리티)를 사용한다.

- Odd Parity: 데이터 비트의 총합이 홀수일 경우 오류가 없는 것으로 판단한다.

- Even Parity: 데이터 비트의 총합이 짝수일 경우 오류가 없는 것으로 판단한다. - Stop Bit: 전송 데이터 패킷의 끝을 정의한다. 1bit 또는 2bit를 사용하며, 1bit 사용시에는 논리값1, 2bit 사용시에는 논리값 0, 1을 순서대로 사용한다.

- OverSampling 방식으로 데이터를 읽어들인다.

- OverSampling 방식은 Baud Rate보다 주파수가 큰 신호를 생성하여 각 데이터 비트의 중앙에서 그 값을 샘플링하는 방식이다.

- 주로 Baud Rate 주파수의 16배가 되는 신호를 생성하여 사용하고, 이 경우 bit counter를 이용하여 8번째 bit count에서 데이터를 샘플링한다.

- UART TX와 RX용으로 사용할 두 개의 와이어만 필요하므로 저렴하다.

- Baud Rate를 이용하여 데이터를 읽는다.

- Baud Rate는 데이터의 전송속도를 나타낸다. 단위는 Bit Per Second(bps)를 사용한다.

- 주로 비동기식 통신에서 Baud Rate를 사용하여 통신이 이루어진다.

- 일반적으로 Baud Rate는 9600bps~115200bps를 사용한다.

- 통신하는 UART 간의 Baud Rate는 일치해야 한다.

- 고속 통신에는 적합하지 않다.

UART 통신 순서

- UART의 TX와 RX간 데이터가 전송되지 않을 때에는 신호가 1로 유지된다. 데이터가 전송되기 위해서 Start Bit가 논리값 0으로 1CLK동안 바뀌며 통신의 시작을 알린다.

- UART RX가 LOW값의 신호를 감지하면 미리 정해진 Baud Rate를 따라 데이터 프레임 비트를 읽기 시작한다. 데이터 프레임 비트의 크기도 미리 약속하여 통신한다

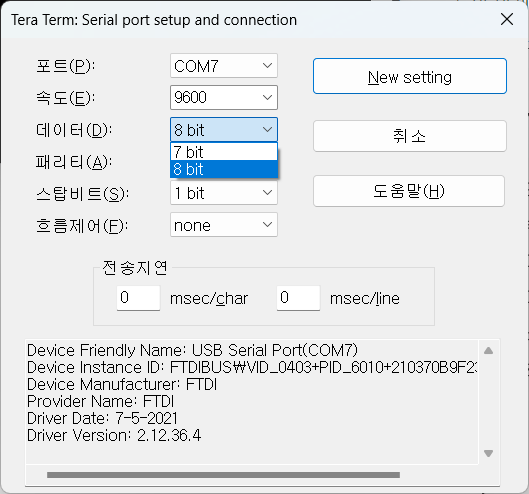

Harman 세미콘 아카데미 교육 과정에서 통신을 위해 사용한 TeraTerm 프로그램에서는 위와 같이 시리얼 포트 설정을 할 수 있다. - 데이터 프레임 비트는 최하위 비트(LSB, Least Significant Bit)부터 전송된다. 크기는 최대 9비트로 제한된다.

- 데이터 비트가 전송된 뒤 패리티 비트가 전송되며, 이를 통해 오류를 검사한다.

-

TeraTerm 프로그램에서는 패리티 비트도 설정할 수 있다.

-

- 패리티 비트의 전송외 완료되면 1Bit 혹은 2Bit의 Stop Bit가 전송되며 통신이 완료된다.

- 통신이 완료되면 UART RX에서 Start Bit, Parity Bit, Stop Bit를 제외한 데이터 패킷만을 병렬로 전환하여 데이터 버스로 전송한다.

UART 설계 과정

1. Baud Rate Generator 설계

UART 설계(1) - Baud Rate Generator 설계

Baud Rate을 생성하고, Over Sampling을 하기 위한 코드 작성 (baud_rate_gen.v)oversampling을 위해 bit count를 진행해야 한다.첫 신호에서 start bit가 들어오면 bit_cnt_std 8번째에 샘플링을 시작하고, 그 이후부터

semicon-circuit.tistory.com

2. UART TX 설계

UART 설계(2) - UART TX 설계

UART TX 모듈 설계 신호 개요DIN [7:0]: 데이터 버스로부터 받는 8비트의 parallel 데이터묶음Send: 데이터 전송의 시작을 명령하는 신호Dout: RX로 전달되는 serial 데이터Busy: UART TX가 동작중임을 나타내는

semicon-circuit.tistory.com

3. UART RX 설계

UART 설계(3) - UART RX 설계 / 최종 설계 완료

FSM 순서idle: din이 1로 유지될 때 대기상태. din이 0이 되면 enable 신호에 맞춰 load로 상태 변경load: 8비트의 데이터를 받은 뒤 parity를 읽고, parity check로 상태 변경parity check: 저장한 parity bit와 data bit

semicon-circuit.tistory.com

'자습시간 > Verilog' 카테고리의 다른 글

| Verilog 복습 프로젝트(1) - 7세그먼트 제어 (0) | 2025.02.11 |

|---|---|

| Verilog 복습 프로젝트 - 스탑워치 / 계산기 / 타이머 / Pmod OLED (0) | 2025.02.11 |

| UART 설계(3) - UART RX 설계 / 최종 설계 완료 (0) | 2024.07.29 |

| UART 설계(2) - UART TX 설계 (0) | 2024.07.26 |