방학동안 verilog 복습을 진행하며 기본적인 하드웨어부터 구현해보고, 이후 pmod OLED를 활용한 장치까지 구현할 예정입니다.

프로젝트 개요

- 기간: 2025.01.20~2025.02.28 (약 1개월)

- 목적: verilog를 이용한 하드웨어 설계 복습 및 SoC, IP에 대한 이해

- 목표: 7세그먼트, 키패드, 버튼, OLED 디스플레이 등을 활용한 스탑워치, 계산기 등 하드웨어 설계

하드웨어 구성

1. 모드 표시 LED: 모드에 따라 LED의 색, 위치가 변함

2. 스탑워치 Start/Stop 버튼

3. 스탑워치 Reset 버튼

4. 모드 변경 버튼

5. 7세그먼트 디스플레이

6. 계산기 키패드

7. Pmod OLED 디스플레이

FPGA 보드: Digilent Cora Z7

기존에 반도체 설계교육에서 사용하던 Digilent사의 Cora Z7을 활용합니다. 이번에 복습을 진행하며 설계 교육에서는 핀 설정 시 직접 schematic을 찾아보았는데, master xdc파일을 찾아서 버튼이나 LED 등을 매핑할 때는 이 파일을 이용했습니다.

[ Cora Z7-07S Master.xdc ]

## This file is a general .xdc for the Cora Z7-07S Rev. B

## To use it in a project:

## - uncomment the lines corresponding to used pins

## - rename the used ports (in each line, after get_ports) according to the top level signal names in the project

## PL System Clock

#set_property -dict { PACKAGE_PIN H16 IOSTANDARD LVCMOS33 } [get_ports { clk }]; #IO_L13P_T2_MRCC_35 Sch=sysclk

#create_clock -add -name sys_clk_pin -period 8.00 -waveform {0 4} [get_ports { clk }];#set

## RGB LEDs

#set_property -dict { PACKAGE_PIN L15 IOSTANDARD LVCMOS33 } [get_ports { led0_b }]; #IO_L22N_T3_AD7N_35 Sch=led0_b

#set_property -dict { PACKAGE_PIN G17 IOSTANDARD LVCMOS33 } [get_ports { led0_g }]; #IO_L16P_T2_35 Sch=led0_g

#set_property -dict { PACKAGE_PIN N15 IOSTANDARD LVCMOS33 } [get_ports { led0_r }]; #IO_L21P_T3_DQS_AD14P_35 Sch=led0_r

#set_property -dict { PACKAGE_PIN G14 IOSTANDARD LVCMOS33 } [get_ports { led1_b }]; #IO_0_35 Sch=led1_b

#set_property -dict { PACKAGE_PIN L14 IOSTANDARD LVCMOS33 } [get_ports { led1_g }]; #IO_L22P_T3_AD7P_35 Sch=led1_g

#set_property -dict { PACKAGE_PIN M15 IOSTANDARD LVCMOS33 } [get_ports { led1_r }]; #IO_L23N_T3_35 Sch=led1_r

## Buttons

#set_property -dict { PACKAGE_PIN D20 IOSTANDARD LVCMOS33 } [get_ports { btn[0] }]; #IO_L4N_T0_35 Sch=btn[0]

#set_property -dict { PACKAGE_PIN D19 IOSTANDARD LVCMOS33 } [get_ports { btn[1] }]; #IO_L4P_T0_35 Sch=btn[1]

## Pmod Header JA

#set_property -dict { PACKAGE_PIN Y18 IOSTANDARD LVCMOS33 } [get_ports { ja[0] }]; #IO_L17P_T2_34 Sch=ja_p[1]

#set_property -dict { PACKAGE_PIN Y19 IOSTANDARD LVCMOS33 } [get_ports { ja[1] }]; #IO_L17N_T2_34 Sch=ja_n[1]

#set_property -dict { PACKAGE_PIN Y16 IOSTANDARD LVCMOS33 } [get_ports { ja[2] }]; #IO_L7P_T1_34 Sch=ja_p[2]

#set_property -dict { PACKAGE_PIN Y17 IOSTANDARD LVCMOS33 } [get_ports { ja[3] }]; #IO_L7N_T1_34 Sch=ja_n[2]

#set_property -dict { PACKAGE_PIN U18 IOSTANDARD LVCMOS33 } [get_ports { ja[4] }]; #IO_L12P_T1_MRCC_34 Sch=ja_p[3]

#set_property -dict { PACKAGE_PIN U19 IOSTANDARD LVCMOS33 } [get_ports { ja[5] }]; #IO_L12N_T1_MRCC_34 Sch=ja_n[3]

#set_property -dict { PACKAGE_PIN W18 IOSTANDARD LVCMOS33 } [get_ports { ja[6] }]; #IO_L22P_T3_34 Sch=ja_p[4]

#set_property -dict { PACKAGE_PIN W19 IOSTANDARD LVCMOS33 } [get_ports { ja[7] }]; #IO_L22N_T3_34 Sch=ja_n[4]

## Pmod Header JB

#set_property -dict { PACKAGE_PIN W14 IOSTANDARD LVCMOS33 } [get_ports { jb[0] }]; #IO_L8P_T1_34 Sch=jb_p[1]

#set_property -dict { PACKAGE_PIN Y14 IOSTANDARD LVCMOS33 } [get_ports { jb[1] }]; #IO_L8N_T1_34 Sch=jb_n[1]

#set_property -dict { PACKAGE_PIN T11 IOSTANDARD LVCMOS33 } [get_ports { jb[2] }]; #IO_L1P_T0_34 Sch=jb_p[2]

#set_property -dict { PACKAGE_PIN T10 IOSTANDARD LVCMOS33 } [get_ports { jb[3] }]; #IO_L1N_T0_34 Sch=jb_n[2]

#set_property -dict { PACKAGE_PIN V16 IOSTANDARD LVCMOS33 } [get_ports { jb[4] }]; #IO_L18P_T2_34 Sch=jb_p[3]

#set_property -dict { PACKAGE_PIN W16 IOSTANDARD LVCMOS33 } [get_ports { jb[5] }]; #IO_L18N_T2_34 Sch=jb_n[3]

#set_property -dict { PACKAGE_PIN V12 IOSTANDARD LVCMOS33 } [get_ports { jb[6] }]; #IO_L4P_T0_34 Sch=jb_p[4]

#set_property -dict { PACKAGE_PIN W13 IOSTANDARD LVCMOS33 } [get_ports { jb[7] }]; #IO_L4N_T0_34 Sch=jb_n[4]

## Crypto SDA

#set_property -dict { PACKAGE_PIN J15 IOSTANDARD LVCMOS33 } [get_ports { crypto_sda }];

## Dedicated Analog Inputs

#set_property -dict { PACKAGE_PIN K9 IOSTANDARD LVCMOS33 } [get_ports { Vp_Vn_0_v_p }]; #VP_0 Sch=xadc_v_p

#set_property -dict { PACKAGE_PIN L10 IOSTANDARD LVCMOS33 } [get_ports { Vp_Vn_0_v_n }]; #VN_0 Sch=xadc_v_n

## ChipKit Outer Analog Header - as Single-Ended Analog Inputs

## NOTE: These ports can be used as single-ended analog inputs with voltages from 0-3.3V (ChipKit analog pins A0-A5) or as digital I/O.

## WARNING: Do not use both sets of constraints at the same time!

#set_property -dict { PACKAGE_PIN E17 IOSTANDARD LVCMOS33 } [get_ports { Vaux1_0_v_p }]; #IO_L3P_T0_DQS_AD1P_35 Sch=ck_an_p[0]

#set_property -dict { PACKAGE_PIN D18 IOSTANDARD LVCMOS33 } [get_ports { Vaux1_0_v_n }]; #IO_L3N_T0_DQS_AD1N_35 Sch=ck_an_n[0]

#set_property -dict { PACKAGE_PIN E18 IOSTANDARD LVCMOS33 } [get_ports { Vaux9_0_v_p }]; #IO_L5P_T0_AD9P_35 Sch=ck_an_p[1]

#set_property -dict { PACKAGE_PIN E19 IOSTANDARD LVCMOS33 } [get_ports { Vaux9_0_v_n }]; #IO_L5N_T0_AD9N_35 Sch=ck_an_n[1]

#set_property -dict { PACKAGE_PIN K14 IOSTANDARD LVCMOS33 } [get_ports { Vaux6_0_v_p }]; #IO_L20P_T3_AD6P_35 Sch=ck_an_p[2]

#set_property -dict { PACKAGE_PIN J14 IOSTANDARD LVCMOS33 } [get_ports { Vaux6_0_v_n }]; #IO_L20N_T3_AD6N_35 Sch=ck_an_n[2]

#set_property -dict { PACKAGE_PIN K16 IOSTANDARD LVCMOS33 } [get_ports { Vaux15_0_v_p }]; #IO_L24P_T3_AD15P_35 Sch=ck_an_p[3]

#set_property -dict { PACKAGE_PIN J16 IOSTANDARD LVCMOS33 } [get_ports { Vaux15_0_v_n }]; #IO_L24N_T3_AD15N_35 Sch=ck_an_n[3]

#set_property -dict { PACKAGE_PIN J20 IOSTANDARD LVCMOS33 } [get_ports { Vaux5_0_v_p }]; #IO_L17P_T2_AD5P_35 Sch=ck_an_p[4]

#set_property -dict { PACKAGE_PIN H20 IOSTANDARD LVCMOS33 } [get_ports { Vaux5_0_v_n }]; #IO_L17N_T2_AD5N_35 Sch=ck_an_n[4]

#set_property -dict { PACKAGE_PIN G19 IOSTANDARD LVCMOS33 } [get_ports { Vaux13_0_v_p }]; #IO_L18P_T2_AD13P_35 Sch=ck_an_p[5]

#set_property -dict { PACKAGE_PIN G20 IOSTANDARD LVCMOS33 } [get_ports { Vaux13_0_v_n }]; #IO_L18N_T2_AD13N_35 Sch=ck_an_n[5]

## ChipKit Outer Analog Header - as Digital I/O

## NOTE: The following constraints should be used when using these ports as digital I/O.

#set_property -dict { PACKAGE_PIN F17 IOSTANDARD LVCMOS33 } [get_ports { ck_a0 }]; #IO_L6N_T0_VREF_35 Sch=ck_a[0]

#set_property -dict { PACKAGE_PIN J19 IOSTANDARD LVCMOS33 } [get_ports { ck_a1 }]; #IO_L10N_T1_AD11N_35 Sch=ck_a[1]

#set_property -dict { PACKAGE_PIN K17 IOSTANDARD LVCMOS33 } [get_ports { ck_a2 }]; #IO_L12P_T1_MRCC_35 Sch=ck_a[2]

#set_property -dict { PACKAGE_PIN L16 IOSTANDARD LVCMOS33 } [get_ports { ck_a3 }]; #IO_L11P_T1_SRCC_35 Sch=ck_a[3]

#set_property -dict { PACKAGE_PIN N16 IOSTANDARD LVCMOS33 } [get_ports { ck_a4 }]; #IO_L21N_T3_DQS_AD14N_35 Sch=ck_a[4]

#set_property -dict { PACKAGE_PIN P14 IOSTANDARD LVCMOS33 } [get_ports { ck_a5 }]; #IO_L6P_T0_34 Sch=ck_a[5]

## ChipKit Inner Analog Header - as Differential Analog Inputs

## NOTE: These ports can be used as differential analog inputs with voltages from 0-1.0V (ChipKit analog pins A6-A11) or as digital I/O.

## WARNING: Do not use both sets of constraints at the same time!

#set_property -dict { PACKAGE_PIN C20 IOSTANDARD LVCMOS33 } [get_ports { Vaux0_0_v_p }]; #IO_L1P_T0_AD0P_35 Sch=ad_p[0]

#set_property -dict { PACKAGE_PIN B20 IOSTANDARD LVCMOS33 } [get_ports { Vaux0_0_v_n }]; #IO_L1N_T0_AD0N_35 Sch=ad_n[0]

#set_property -dict { PACKAGE_PIN F19 IOSTANDARD LVCMOS33 } [get_ports { Vaux12_0_v_p }]; #IO_L15P_T2_DQS_AD12P_35 Sch=ad_p[12]

#set_property -dict { PACKAGE_PIN F20 IOSTANDARD LVCMOS33 } [get_ports { Vaux12_0_v_n }]; #IO_L15N_T2_DQS_AD12N_35 Sch=ad_n[12]

#set_property -dict { PACKAGE_PIN B19 IOSTANDARD LVCMOS33 } [get_ports { Vaux8_0_v_p }]; #IO_L2P_T0_AD8P_35 Sch=ad_p[8]

#set_property -dict { PACKAGE_PIN A20 IOSTANDARD LVCMOS33 } [get_ports { Vaux8_0_v_n }]; #IO_L2N_T0_AD8N_35 Sch=ad_n[8]

## ChipKit Inner Analog Header - as Digital I/O

## NOTE: The following constraints should be used when using the inner analog header ports as digital I/O.

#set_property -dict { PACKAGE_PIN C20 IOSTANDARD LVCMOS33 } [get_ports { ck_a6 }]; #IO_L1P_T0_AD0P_35 Sch=ad_p[0]

#set_property -dict { PACKAGE_PIN B20 IOSTANDARD LVCMOS33 } [get_ports { ck_a7 }]; #IO_L1N_T0_AD0N_35 Sch=ad_n[0]

#set_property -dict { PACKAGE_PIN F19 IOSTANDARD LVCMOS33 } [get_ports { ck_a8 }]; #IO_L15P_T2_DQS_AD12P_35 Sch=ad_p[12]

#set_property -dict { PACKAGE_PIN F20 IOSTANDARD LVCMOS33 } [get_ports { ck_a9 }]; #IO_L15N_T2_DQS_AD12N_35 Sch=ad_n[12]

#set_property -dict { PACKAGE_PIN B19 IOSTANDARD LVCMOS33 } [get_ports { ck_a10 }]; #IO_L2P_T0_AD8P_35 Sch=ad_p[8]

#set_property -dict { PACKAGE_PIN A20 IOSTANDARD LVCMOS33 } [get_ports { ck_a11 }]; #IO_L2N_T0_AD8N_35 Sch=ad_n[8]

## ChipKit Outer Digital Header

#set_property -dict { PACKAGE_PIN U14 IOSTANDARD LVCMOS33 } [get_ports { ck_io0 }]; #IO_L11P_T1_SRCC_34 Sch=ck_io[0]

#set_property -dict { PACKAGE_PIN V13 IOSTANDARD LVCMOS33 } [get_ports { ck_io1 }]; #IO_L3N_T0_DQS_34 Sch=ck_io[1]

#set_property -dict { PACKAGE_PIN T14 IOSTANDARD LVCMOS33 } [get_ports { ck_io2 }]; #IO_L5P_T0_34 Sch=ck_io[2]

#set_property -dict { PACKAGE_PIN T15 IOSTANDARD LVCMOS33 } [get_ports { ck_io3 }]; #IO_L5N_T0_34 Sch=ck_io[3]

#set_property -dict { PACKAGE_PIN V17 IOSTANDARD LVCMOS33 } [get_ports { ck_io4 }]; #IO_L21P_T3_DQS_34 Sch=ck_io[4]

#set_property -dict { PACKAGE_PIN V18 IOSTANDARD LVCMOS33 } [get_ports { ck_io5 }]; #IO_L21N_T3_DQS_34 Sch=ck_io[5]

#set_property -dict { PACKAGE_PIN R17 IOSTANDARD LVCMOS33 } [get_ports { ck_io6 }]; #IO_L19N_T3_VREF_34 Sch=ck_io[6]

#set_property -dict { PACKAGE_PIN R14 IOSTANDARD LVCMOS33 } [get_ports { ck_io7 }]; #IO_L6N_T0_VREF_34 Sch=ck_io[7]

#set_property -dict { PACKAGE_PIN N18 IOSTANDARD LVCMOS33 } [get_ports { ck_io8 }]; #IO_L13P_T2_MRCC_34 Sch=ck_io[8]

#set_property -dict { PACKAGE_PIN M18 IOSTANDARD LVCMOS33 } [get_ports { ck_io9 }]; #IO_L8N_T1_AD10N_35 Sch=ck_io[9]

#set_property -dict { PACKAGE_PIN U15 IOSTANDARD LVCMOS33 } [get_ports { ck_io10 }]; #IO_L11N_T1_SRCC_34 Sch=ck_io[10]

#set_property -dict { PACKAGE_PIN K18 IOSTANDARD LVCMOS33 } [get_ports { ck_io11 }]; #IO_L12N_T1_MRCC_35 Sch=ck_io[11]

#set_property -dict { PACKAGE_PIN J18 IOSTANDARD LVCMOS33 } [get_ports { ck_io12 }]; #IO_L14P_T2_AD4P_SRCC_35 Sch=ck_io[12]

#set_property -dict { PACKAGE_PIN G15 IOSTANDARD LVCMOS33 } [get_ports { ck_io13 }]; #IO_L19N_T3_VREF_35 Sch=ck_io[13]

## ChipKit Inner Digital Header

#set_property -dict { PACKAGE_PIN R16 IOSTANDARD LVCMOS33 } [get_ports { ck_io26 }]; #IO_L19P_T3_34 Sch=ck_io[26]

#set_property -dict { PACKAGE_PIN U12 IOSTANDARD LVCMOS33 } [get_ports { ck_io27 }]; #IO_L2N_T0_34 Sch=ck_io[27]

#set_property -dict { PACKAGE_PIN U13 IOSTANDARD LVCMOS33 } [get_ports { ck_io28 }]; #IO_L3P_T0_DQS_PUDC_B_34 Sch=ck_io[28]

#set_property -dict { PACKAGE_PIN V15 IOSTANDARD LVCMOS33 } [get_ports { ck_io29 }]; #IO_L10P_T1_34 Sch=ck_io[29]

#set_property -dict { PACKAGE_PIN T16 IOSTANDARD LVCMOS33 } [get_ports { ck_io30 }]; #IO_L9P_T1_DQS_34 Sch=ck_io[30]

#set_property -dict { PACKAGE_PIN U17 IOSTANDARD LVCMOS33 } [get_ports { ck_io31 }]; #IO_L9N_T1_DQS_34 Sch=ck_io[31]

#set_property -dict { PACKAGE_PIN T17 IOSTANDARD LVCMOS33 } [get_ports { ck_io32 }]; #IO_L20P_T3_34 Sch=ck_io[32]

#set_property -dict { PACKAGE_PIN R18 IOSTANDARD LVCMOS33 } [get_ports { ck_io33 }]; #IO_L20N_T3_34 Sch=ck_io[33]

#set_property -dict { PACKAGE_PIN P18 IOSTANDARD LVCMOS33 } [get_ports { ck_io34 }]; #IO_L23N_T3_34 Sch=ck_io[34]

#set_property -dict { PACKAGE_PIN N17 IOSTANDARD LVCMOS33 } [get_ports { ck_io35 }]; #IO_L23P_T3_34 Sch=ck_io[35]

#set_property -dict { PACKAGE_PIN M17 IOSTANDARD LVCMOS33 } [get_ports { ck_io36 }]; #IO_L8P_T1_AD10P_35 Sch=ck_io[36]

#set_property -dict { PACKAGE_PIN L17 IOSTANDARD LVCMOS33 } [get_ports { ck_io37 }]; #IO_L11N_T1_SRCC_35 Sch=ck_io[37]

#set_property -dict { PACKAGE_PIN H17 IOSTANDARD LVCMOS33 } [get_ports { ck_io38 }]; #IO_L13N_T2_MRCC_35 Sch=ck_io[38]

#set_property -dict { PACKAGE_PIN H18 IOSTANDARD LVCMOS33 } [get_ports { ck_io39 }]; #IO_L14N_T2_AD4N_SRCC_35 Sch=ck_io[39]

#set_property -dict { PACKAGE_PIN G18 IOSTANDARD LVCMOS33 } [get_ports { ck_io40 }]; #IO_L16N_T2_35 Sch=ck_io[40]

#set_property -dict { PACKAGE_PIN L20 IOSTANDARD LVCMOS33 } [get_ports { ck_io41 }]; #IO_L9N_T1_DQS_AD3N_35 Sch=ck_io[41]

## ChipKit SPI

#set_property -dict { PACKAGE_PIN W15 IOSTANDARD LVCMOS33 } [get_ports { ck_miso }]; #IO_L10N_T1_34 Sch=ck_miso

#set_property -dict { PACKAGE_PIN T12 IOSTANDARD LVCMOS33 } [get_ports { ck_mosi }]; #IO_L2P_T0_34 Sch=ck_mosi

#set_property -dict { PACKAGE_PIN H15 IOSTANDARD LVCMOS33 } [get_ports { ck_sck }]; #IO_L19P_T3_35 Sch=ck_sck

#set_property -dict { PACKAGE_PIN F16 IOSTANDARD LVCMOS33 } [get_ports { ck_ss }]; #IO_L6P_T0_35 Sch=ck_ss

## ChipKit I2C

#set_property -dict { PACKAGE_PIN P16 IOSTANDARD LVCMOS33 } [get_ports { ck_scl }]; #IO_L24N_T3_34 Sch=ck_scl

#set_property -dict { PACKAGE_PIN P15 IOSTANDARD LVCMOS33 } [get_ports { ck_sda }]; #IO_L24P_T3_34 Sch=ck_sda

##Misc. ChipKit signals

#set_property -dict { PACKAGE_PIN M20 IOSTANDARD LVCMOS33 } [get_ports { ck_ioa }]; #IO_L7N_T1_AD2N_35 Sch=ck_ioa

## User Digital I/O Header J1

#set_property -dict { PACKAGE_PIN L19 IOSTANDARD LVCMOS33 } [get_ports { user_dio[1] }]; #IO_L9P_T1_DQS_AD3P_35 Sch=user_dio[1]

#set_property -dict { PACKAGE_PIN M19 IOSTANDARD LVCMOS33 } [get_ports { user_dio[2] }]; #IO_L7P_T1_AD2P_35 Sch=user_dio[2]

#set_property -dict { PACKAGE_PIN N20 IOSTANDARD LVCMOS33 } [get_ports { user_dio[3] }]; #IO_L14P_T2_SRCC_34 Sch=user_dio[3]

#set_property -dict { PACKAGE_PIN P20 IOSTANDARD LVCMOS33 } [get_ports { user_dio[4] }]; #IO_L14N_T2_SRCC_34 Sch=user_dio[4]

#set_property -dict { PACKAGE_PIN P19 IOSTANDARD LVCMOS33 } [get_ports { user_dio[5] }]; #IO_L13N_T2_MRCC_34 Sch=user_dio[5]

#set_property -dict { PACKAGE_PIN R19 IOSTANDARD LVCMOS33 } [get_ports { user_dio[6] }]; #IO_0_34 Sch=user_dio[6]

#set_property -dict { PACKAGE_PIN T20 IOSTANDARD LVCMOS33 } [get_ports { user_dio[7] }]; #IO_L15P_T2_DQS_34 Sch=user_dio[7]

#set_property -dict { PACKAGE_PIN T19 IOSTANDARD LVCMOS33 } [get_ports { user_dio[8] }]; #IO_25_34 Sch=user_dio[8]

#set_property -dict { PACKAGE_PIN U20 IOSTANDARD LVCMOS33 } [get_ports { user_dio[9] }]; #IO_L15N_T2_DQS_34 Sch=user_dio[9]

#set_property -dict { PACKAGE_PIN V20 IOSTANDARD LVCMOS33 } [get_ports { user_dio[10] }]; #IO_L16P_T2_34 Sch=user_dio[10]

#set_property -dict { PACKAGE_PIN W20 IOSTANDARD LVCMOS33 } [get_ports { user_dio[11] }]; #IO_L16N_T2_34 Sch=user_dio[11]

#set_property -dict { PACKAGE_PIN K19 IOSTANDARD LVCMOS33 } [get_ports { user_dio[12] }]; #IO_L10P_T1_AD11P_35 Sch=user_dio[12]

7세그먼트 디스플레이: WCN4-0056SR-C11R

스탑워치나 계산기에서 숫자를 표시하기 위해 네자리 7세그먼트 디스플레이를 사용했습니다. 내부 회로는 아래와 같이 구성되어 있으며, verilog를 활용한 제어 방식은 아래 게시물에서 설명합니다.

Verilog 복습 프로젝트(1) - 7세그먼트 제어

스탑워치를 설계하기에 앞서, 숫자를 표시하기 위한 네자리 7세그먼트 디스플레이를 제어하기 위한 코드를 작성했습니다.이번에 사용한 디스플레이는 이전에 반도체 설계교육 중 임베디드 시

semicon-circuit.tistory.com

16자리 키패드: [Digilent] Pmod KYPD (16-button Keypad 410-195)

계산기 모드에서 숫자 입력 시 사용할 키패드는 Digilent사의 Pmod KYPD를 이용했습니다.

행을 입력으로, 열을 출력으로 설정한 뒤 스캔하고자 하는 열만 LOW로 설정했습니다. 이 때 버튼을 누르면 LOW값이 버튼의 행으로 전달되어 어느 위치의 버튼이 눌렸는지 파악할 수 있습니다.

Verilog 복습 프로젝트(3) - Decoder 설계 [Pmod KYPD 이용]

계산기를 설계할 때에는 Digilent의 Pmod KYPD를 통해 값을 입력받아 숫자나 문자로 변환하는 Decoder와 Decoder로부터 받은 값을 연산하여 세그먼트 디스플레이로 보내기 위한 calculator 모듈이 필요합니

semicon-circuit.tistory.com

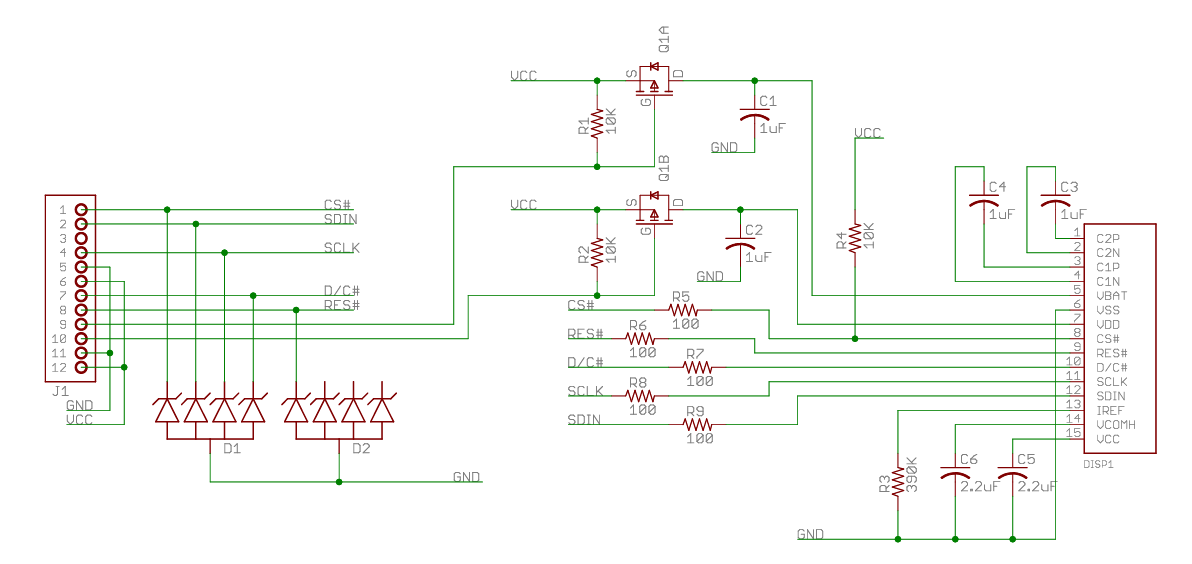

Pmod OLED: [Digilent] 128 x 32 Pixel Monochromatic OLED Display 410-222

추후 OLED를 활용해 현재 모드를 표시하거나, 간단한 게임을 구현하거나 모드를 표시하기 위해 활용할 예정입니다.

설계 진행 상황 업데이트

2025.01.26 | 세그먼트, 4x4버튼 제어(이후 Pmod KYPD로 변경)

2025.01.28 | 스탑워치 완료

2025.02.09 | 계산기 완료

Mode 1: x [ Left LED_R ]

Mode 2: 스탑워치 [ Left LED_B ]

Mode 3: 계산기 [ Right LED_R ]

Mode 4: x [ Right LED_B ]

top module [ 2025.02.09 ]

`timescale 1ns / 1ps

module top(

input RST,

input CLK,

input BTN0,

input BTN1,

inout [7:0] JA, // Port JA on Nexys3, JA[3:0] is Columns, JA[7:4] is rows

input Y_BTN_IN, //L20

output Y_BTN_HIGH, //G18

output reg [0:3] LED,

output [7:0] SEG,

output [3:0] DIG

);

reg [13:0] VALUE;

wire [13:0] VAL0, VAL1, VAL2, VAL3, CALC_RESULT; //VALUE는 세그먼트 전송 값

reg [1:0] CURR_MODE, NEXT_MODE;

wire btn0_debounced, btn1_debounced, btny_debounced;

//Button Operation

assign Y_BTN_HIGH = 1'b1;

initial begin

CURR_MODE = 2'b0;

VALUE = 0;

end

always @(posedge CLK) begin

CURR_MODE <= NEXT_MODE;

if(btny_debounced) NEXT_MODE <= NEXT_MODE + 1;

case(CURR_MODE)

0: begin //Timer

LED <= 4'b0001; //LED1_R\

VALUE <= VAL0;

end

1: begin //Stopwatch

LED <= 4'b0010; //LED1_B

VALUE <= VAL1;

end

2: begin //Caculator

LED <= 4'b0100; //LED0_R

VALUE <= CALC_RESULT;

end

3: LED <= 4'b1000; //LED0_B

default: LED <= 4'b0000;

endcase

end

wire KEY_PRESSED;

//Instantiation

calculator Calc (.rst (RST), .clk (CLK), .val2 (VAL2), .key_pressed (KEY_PRESSED), .result(CALC_RESULT));

Decoder Decoder ( .rst (RST), .clk(CLK), .row(JA[7:4]), .col(JA[3:0]), .key(VAL2), .pressed_debounce (KEY_PRESSED)); //KYPD to Num Decoder

segment_display Seg_cntrl ( .rst (RST), .clk (CLK), .bcds(VALUE), .mode(CURR_MODE), .segments(SEG), .com_dig (DIG));

debounce debounce0 (.clk (CLK), .reset (RST), .i_btn (BTN0), .o_btn (btn0_debounced));

debounce debounce1 (.clk (CLK), .reset (RST), .i_btn (BTN1), .o_btn (btn1_debounced));

debounce debouncey (.clk (CLK), .reset (RST), .i_btn (Y_BTN_IN), .o_btn (btny_debounced));

stopwatch stopwatch ( .rst(RST), .clk(CLK), .mode(CURR_MODE), .btn1(btn1_debounced), .btn0(btn0_debounced), .value(VAL1));

endmodule'자습시간 > Verilog' 카테고리의 다른 글

| Verilog 복습 프로젝트(2) - 스탑워치 설계 (0) | 2025.02.12 |

|---|---|

| Verilog 복습 프로젝트(1) - 7세그먼트 제어 (0) | 2025.02.11 |

| UART(Universal Asynchronous Receiver/Transmitter) (1) | 2024.07.30 |

| UART 설계(3) - UART RX 설계 / 최종 설계 완료 (0) | 2024.07.29 |