[2024.04.22.월] 인천인력개발원 하만 세미콘 아카데미

전자회로 해석 및 설계

3. Transistor 응용회로

1. Open_Collector 프로젝트 생성

2. 회로 구성

3. 시뮬레이션 실행

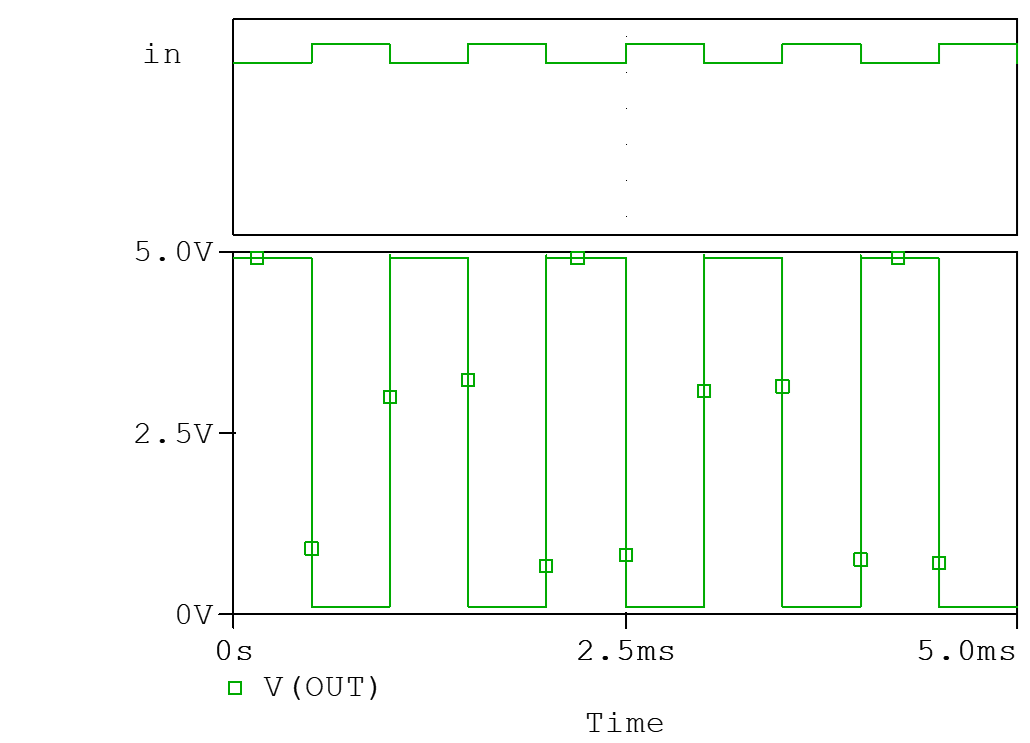

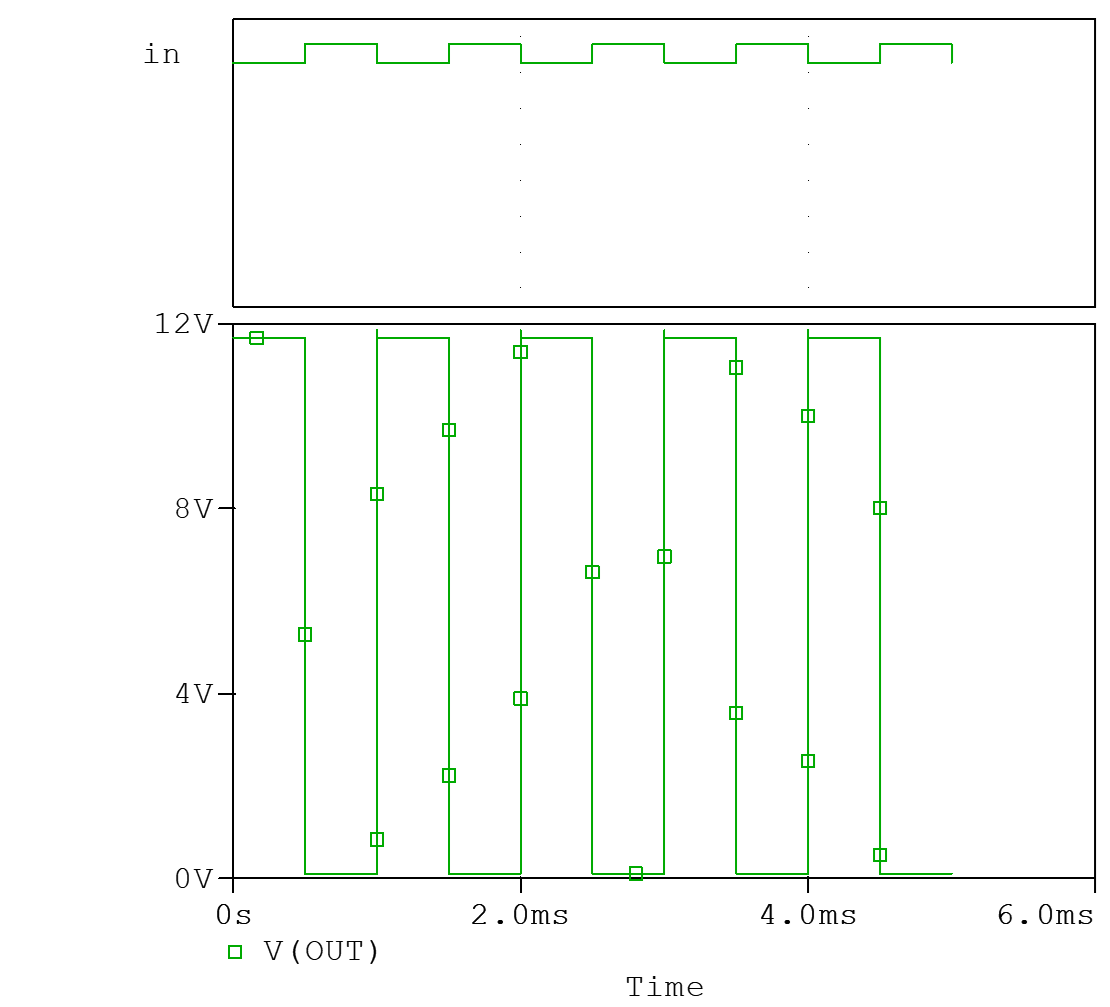

4. Propogation Delay발생: 내부 신호처리 과정에서 발생

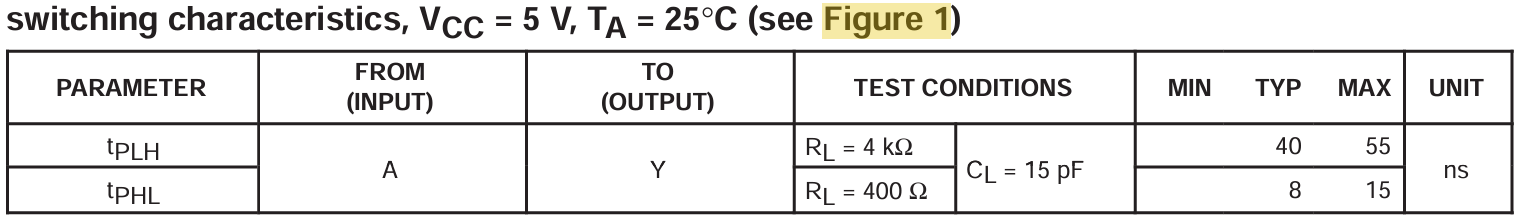

5. 7405/EVAL로 변경

6. 시뮬레이션

- www.ti.com에서 7405 검색, datasheet 다운로드

- HEX: 부품 6개 사용(DUAL, QUAD, HEX, OCTA)

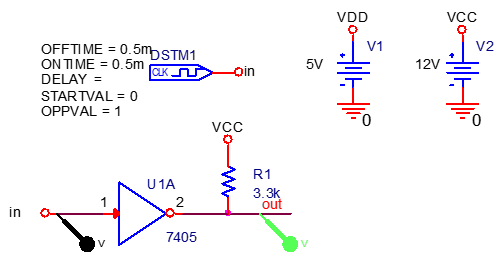

- OPEN-COLLECTOR: 아래 등가회로에서 입력이 HIGH면 OUTPUT에 LOW, 입력이 LOW면 Collector 핀의 OUTPUT이 Floating(Open) 상태

7. 위 등가회로를 참고하여 회로 구성

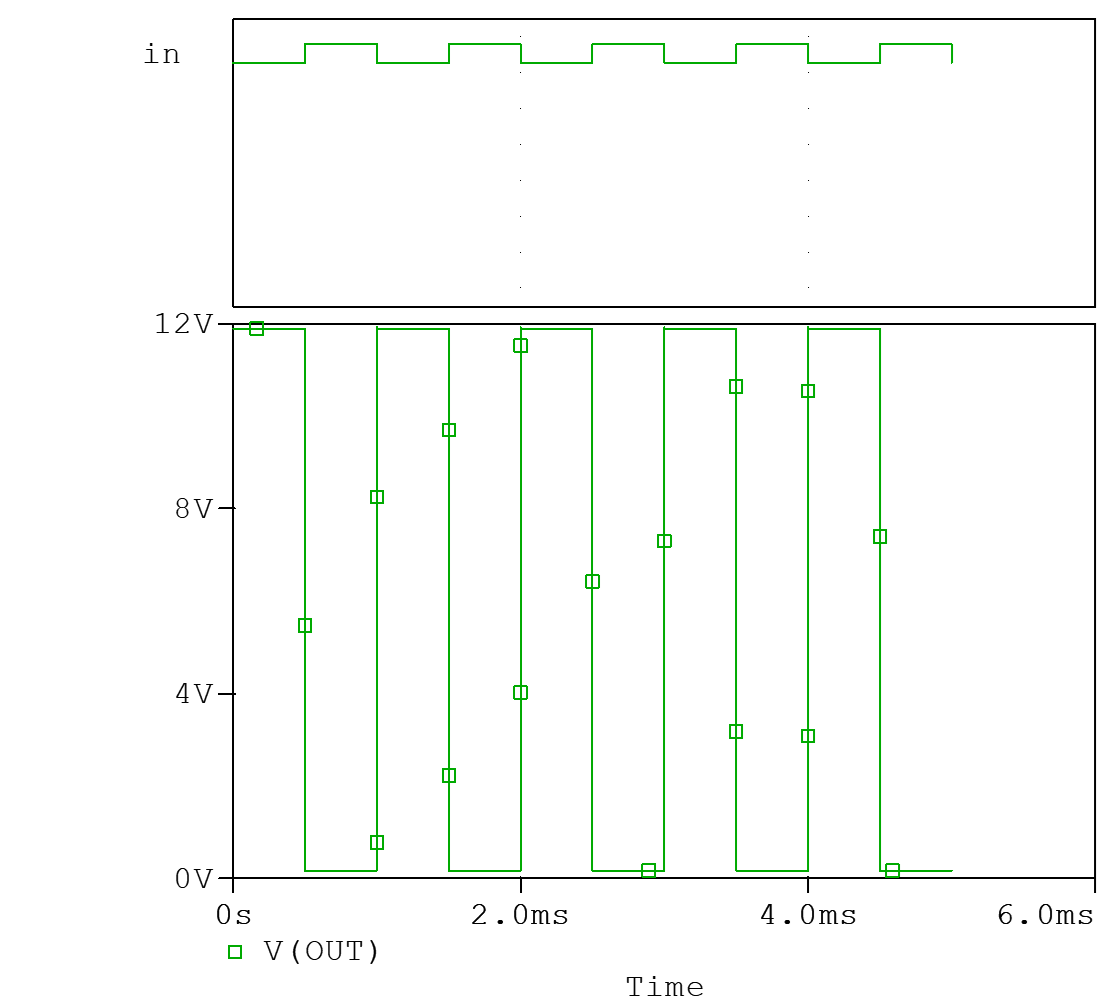

8. Simulation

- OFF에서 0V가 나오지 않는 이유: BJT의 Saturation Voltage로 인함

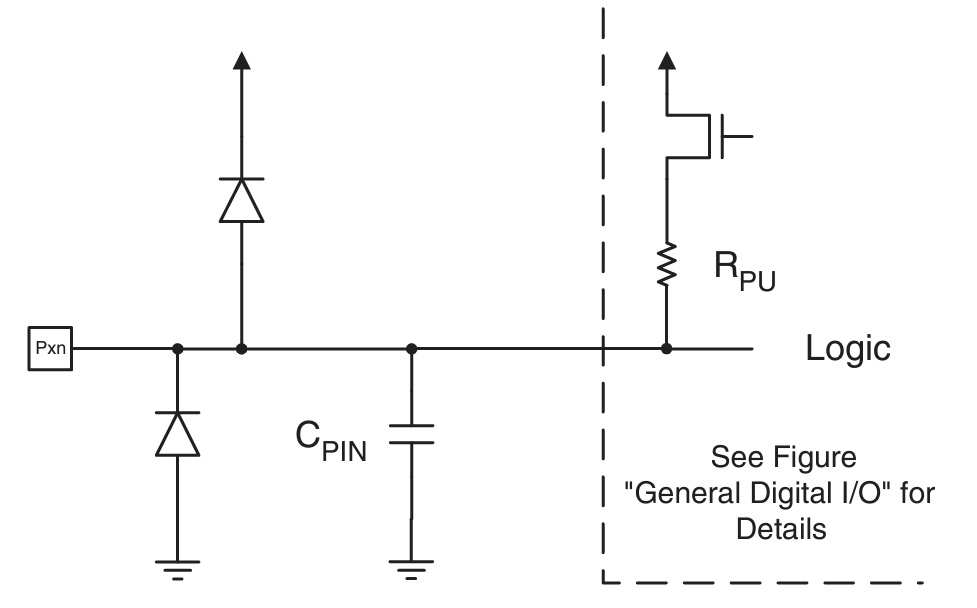

[ ATMega 128 I/O Pin Equivalent Schematic 회로 분석 ]

- 다이오드 2개: ESD 보호용 다이오드

- 캐패시터: 기생 캐패시터 표현

- Pxn: GPIO

- Rpu: Pull-Up 저항

- NMOS: Pxn을 input/output으로 사용 시 이를 결정하기 위해서 필요

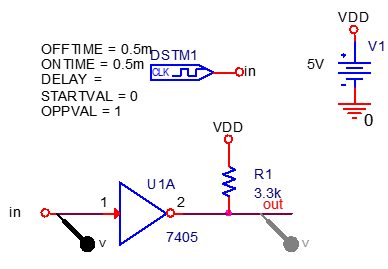

실습2: Pullup 저항 이용 Level Shifter

1. VCC 추가한 뒤 시뮬레이션

2. Pullup 저항을 1k로 변경 후 재시도