[2024.08.23.금] 인천인력개발원 하만 세미콘 아카데미

Introduction

1. Analog 신호와 Digital 신호

- Analog 신호: 자연계에 존재하는 시간에 따라 변화하는 연속적인 신호

ex) 오디오 신호, 밝기, 온도, ... - Digital 신호

- Digit: 한 자리 숫자를 의미

- Digital: 숫자로 표시된

2. Resolution(분해능)

- ADC에서, 8Bit는 분해능이 256, 12Bit는 분해능이 4096, 16Bit는 분해능이 65536이다.

-> Bit 수가 클 수록 분해능이 증가하여 데이터의 정밀도가 증가하지만, 데이터의 크기가 커진다. - 수직 분해능 증가: 데이터의 비트 수를 증가시켜 값을 더 많이 할당

- 수평 분해능 증가: Sampling Clock의 주파수를 증가시켜 값을 취하는 빈도를 높임

3. Digital 회로 설계 시 주의사항

- Glitch(잡음): input 신호간의 시간 차로 인해 발생하는 output 신호의 짧은 잡음

- 조합회로의 출력을 clock으로 사용 금지

- 조합회로의 출력을 FlipFlop의 Input으로 하여 발생되는 출력을 사용하여 Glitch 방지 가능 [ 동기화 설계 ]

- 전달 지연 시간: input이 output으로 출력되기까지 지연되는 시간

- 해결방법: 동기화 설계

- Fan-Out: 한 개의 출력신호에 연결된 입력채널의 수

- 논리게이의 1개의 출력이 3개의 논리게이트의 입력으로 들어가면 Fan-Out 3

- Fan-Out 숫자가 커질수록 Delay가 발생

설계 1: 100진 카운터 설계

[ cnt_100.v ]

더보기

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2024/08/23 11:13:16

// Design Name:

// Module Name: cnt_100

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module cnt_100(

input clk,

input rst,

output reg [6:0] q

);

always@(negedge rst, posedge clk)

begin

if(rst) q <= 0;

else q <= q + 1;

if(q == 99) q <= 0;

end

endmodule[ cnt_100_tb.v ]

더보기

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2024/08/23 11:15:31

// Design Name:

// Module Name: cnt_100_tb

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module cnt_100_tb();

parameter CLK_PD = 8.0;

reg CLK, RST;

wire [6:0] Q;

cnt_100 uut(

.clk (CLK),

.rst (RST),

.q (Q)

);

initial begin

RST = 1'b1;

#(CLK_PD*10);

RST = 1'b0;

end

initial CLK = 1'b0;

always #(CLK_PD/2) CLK = ~CLK;

endmodule[ 테스트벤치 결과 ]

- 전압 조건(외부 조건)이 불안정하여 레지스터(CNT)의 값이 설정하지 않은 값(ex. 105)로 튄 경우: 7Bit인 127까지 증가 후 0으로 복귀

해결 방법: 0으로 복귀하는 조건을 99 이상으로 설장

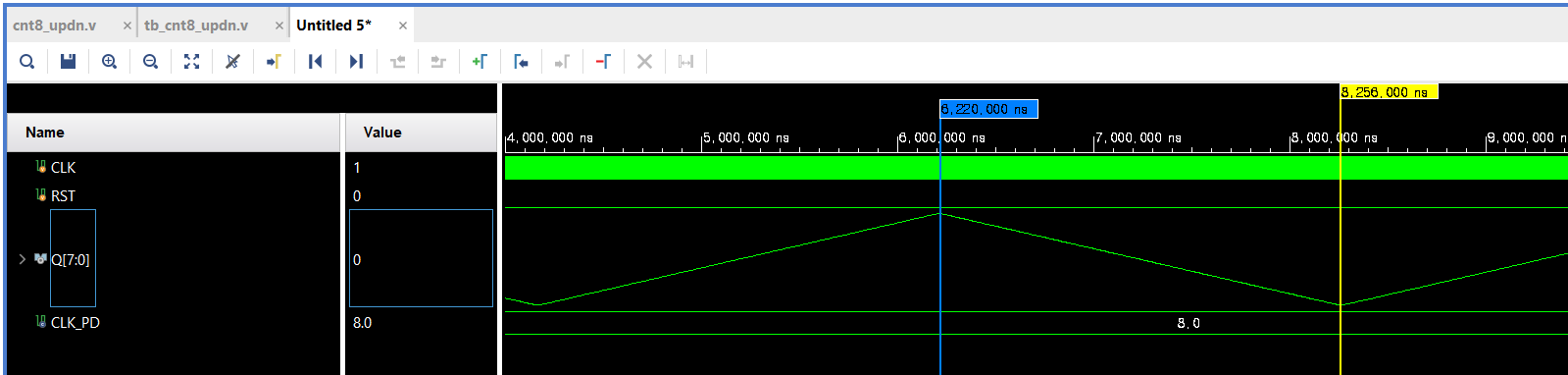

설계 2: 8Bit Up-Down Counter

- 0~255까지 증가 후 다시 255~0으로 감소하는 동작 반복

- input: clk, rst

- output: q[7:0]

- reg up_dn 선언하여 1일 때 up, 0일 때 down으로 동작

[ cnt8_updn.v ]

더보기

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2024/08/23 11:59:00

// Design Name:

// Module Name: cnt8_updn

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module cnt8_updn(

input clk,

input rst,

output reg [7:0] q

);

reg up_dn = 1'b1; //count up when up_dn = 1, count down when up_dn = 0;

always@(negedge rst, posedge clk) begin

if(rst) q=0;

else begin

if(up_dn) begin

if(q >= 255) up_dn <= 0;

else q <= q + 1;

end

else begin

if(q <= 0) up_dn <= 1;

else q <= q - 1;

end

end

end

endmodule[ tb_cnt8_updn.v ]

더보기

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2024/08/23 12:18:02

// Design Name:

// Module Name: tb_cnt8_updn

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module tb_cnt8_updn();

parameter CLK_PD = 8.0;

reg CLK, RST;

wire [7:0] Q;

cnt8_updn uut(

.clk (CLK),

.rst (RST),

.q (Q)

);

initial begin

RST = 1'b1;

#(CLK_PD*10);

RST = 1'b0;

end

initial CLK = 1'b1;

always #(CLK_PD/2) CLK = ~CLK;

endmodule[ 테스트벤치 결과 ]

tcl 파일을 이용하여 시뮬레이션 진행

1. Run Behavioral Simulation 후 나타나는 Objects 탭에서 CLK 우클릭 - Force Clock 클릭

2. Leading edge value를 0, Trailing edge value를 1로 설정 후 주기를 100ns로 변경

3. cnt8_updn.v 파일을 열어 우클릭 - Save File as 클릭 후 ~~.tcl로 확장자 변경 및 저장(File type을 all files로 변경)

...

FPGA(Field Programmable Gate Array)

디자인 순서

1. 착상(구상) 단계

2. 설계사양 작성

- 입/출력 조건

- 구현 알고리즘 수립

- 알고리즘: 어떤 일을 어떤 순서에 따라 어떤 작업을 진행할 지에 대한 작업 절차 정보

3. 회로설계

- FPGA 선정

- Top Down & Bottom Up 설계

- Schematic / HDL(Verilog / VHDL)

4. 모의 실험(Simulation)

- Simulation & Board Implementation

- 실험계획 수립

5. 회로 합성(Synthesis): 타겟 라이브러리로 맵핑

6. 배치 배선(Place & Route)

7. 보드 테스트

- Simulation & Board Implementation

- 실험계획 수립

LUT(Look Up Table)

1. LUT(Look Up Table): XILINX FPGA에서 조합회로를 구현하는 Library

- 1Bit의 출력을 갖는 조합회로 구현

- Artix 7 FPGA는 LUT1~LUT6을 가짐

- LUT1: 입력 1개, 출력 1개 (ex. NOT Gate) -> 2^(2^1) = 4개의 패턴 표현 가능

- LUT2: 입력 2개, 출력 1개(ex. XOR, AND, ... Gate) -> 2^(2^2) = 16개의 패턴 표현 가능

- LUT4: 입력 4개, 출력 1개 -> 2^(2^4) = 2^16개의 패턴 표현 가능

'하만(Harman) 세미콘 반도체 설계 과정' 카테고리의 다른 글

| 직무종합프로젝트 (2) (0) | 2024.08.27 |

|---|---|

| Auto P&R 교육 6일차 (0) | 2024.06.02 |

| Auto P&R 교육 5일차 (0) | 2024.06.02 |

| Auto P&R 교육 4일차 (0) | 2024.05.26 |