ModelSim - Intel FPGA Standard Edition

ModelSim-Intel® FPGAs Standard Edition Software Version 18.1

ModelSim-Intel® FPGAs Standard Edition Software Version 18.1 B625

www.intel.com

ModelSim 명령어

- cd <dir>: change directory

- dir: directory 내용표시

- vlib work: modelsim에서 compile 결과를 저장해둘 directory "work"를 생성

- vlog _____.v: .v 파일의 문법 check&compile

- vsim _____: simulation 시작

- add wave *: 모든 신호를 파형창에 표시

- do ____.do

- --~~; --로 주석 작성

- force: 신호에 값 인가

ex) force clk 0 0, 1 5ns, -r 10ns: clk 신호에 0 값을 0ns 인가 후 1 값을 5ns 인가. 이를 10ns마다 반복(-r)

ex2) force rst 0 0, 1 20ns: 0ns에서 rst값을 0 인가, 20ns 이후부터 1 인가 - run ____ns/us/ms: 설정한 시간만큼 실행

설계 1: 버튼 카운터 설계

- 버튼 카운터 동작

- 보드의 BTN1을 누르면 Segment에 표시된 수가 1씩 증가

- BTN0을 누르면 수가 초기화되어 00이 표시된다.

- module 포트 선언 및 register, wire 선언

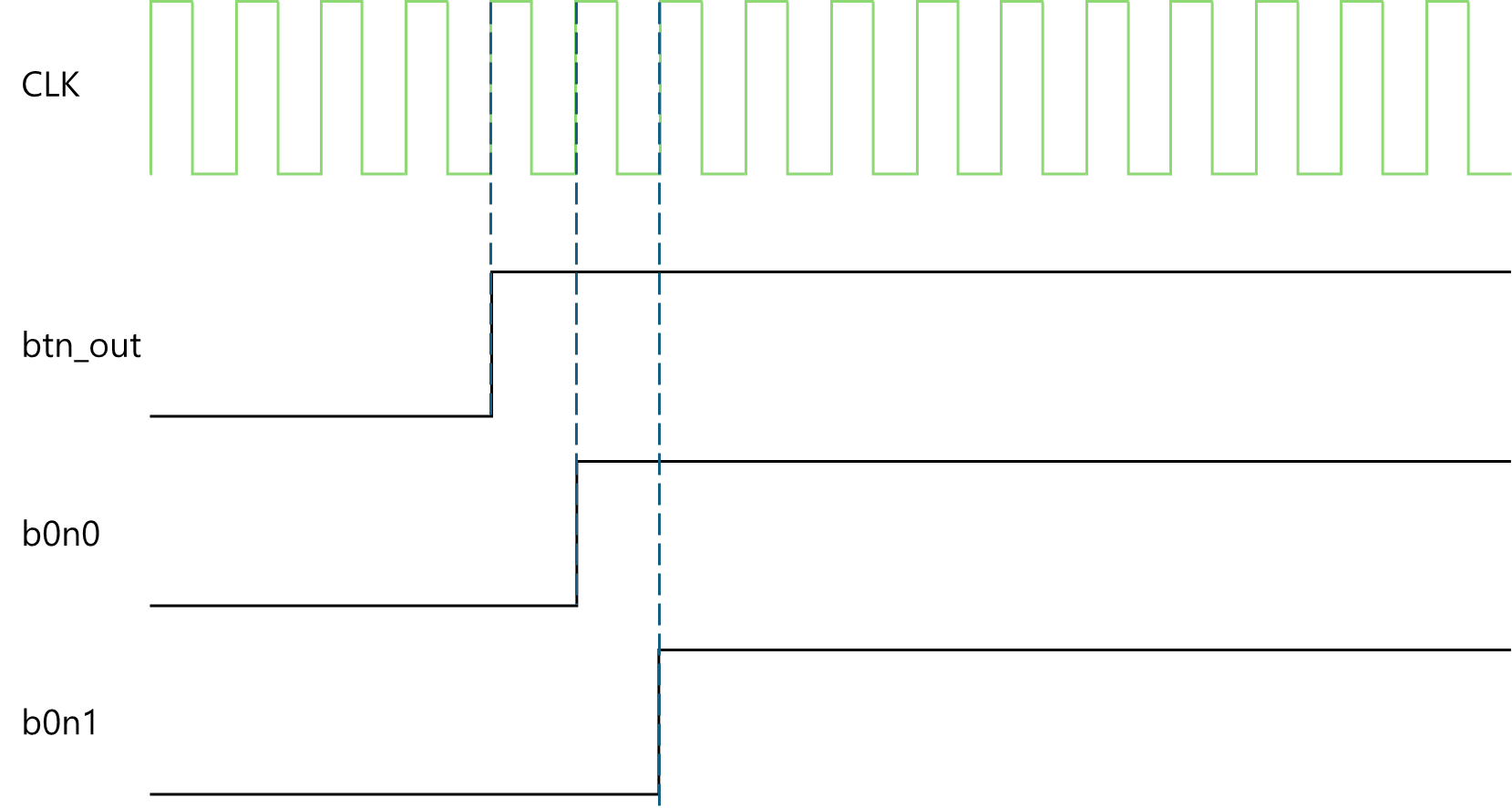

- b0n0, b0n1: Button 동작의 Rising Edge를 파악하는 신호

- btn_cnt: 버튼을 누른 횟수를 저장하기 위한 레지스터(99까지 저장하므로 2^7 필요)

- kcnt: killo count

- pls: pulse

- hexv:

- bcdh, bcdl:

- bcds:

- segd:

- btn_out:

- b0n0, b0n1: Button이 눌릴 시 발생하는 Rising Edge를 파악하기 위한 신호

- btn_out이 b0n0에 인가되고, b0n0이 b0n1이 인가되면 다음과 같은 순서가 생성된다.

1clock씩 밀리며 신호가 생성됨 - Rising Edge에서는 b0n0에 1clk 뒤에 인가된 btn_out의 신호가 1로 나타나고, 이 때 아직 b0n1은 0의 상태가 유지된다. 따라서 b0n0이 1이고, b0n1이 0일 때 버튼이 눌린 rising edge이므로 이 때 btn_cnt를 증가시킨다.

- btn_out이 b0n0에 인가되고, b0n0이 b0n1이 인가되면 다음과 같은 순서가 생성된다.

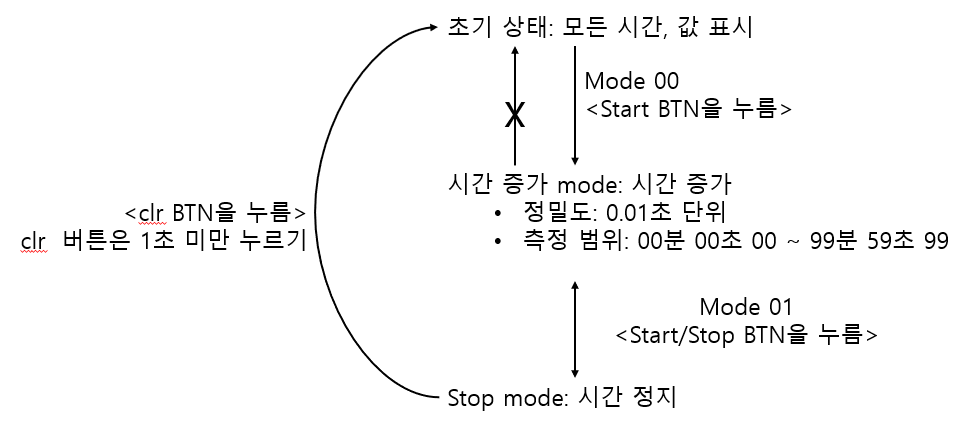

설계 2: 스탑워치 설계

- 분 count: 00~99

- 초 count: 00~59

- under 초 count: 00~99

- 모드(FSM) 설정

- 00: 초기화 모드

- 01: 시간 증가모드

'하만(Harman) 세미콘 반도체 설계 과정' 카테고리의 다른 글

| 직무종합 프로젝트 (1) (0) | 2024.08.23 |

|---|---|

| Auto P&R 교육 6일차 (0) | 2024.06.02 |

| Auto P&R 교육 5일차 (0) | 2024.06.02 |

| Auto P&R 교육 4일차 (0) | 2024.05.26 |