[2024.04.24.수] 인천인력개발원 하만 세미콘 아카데미

CMOS 공정

1. CMOS 공정 종류

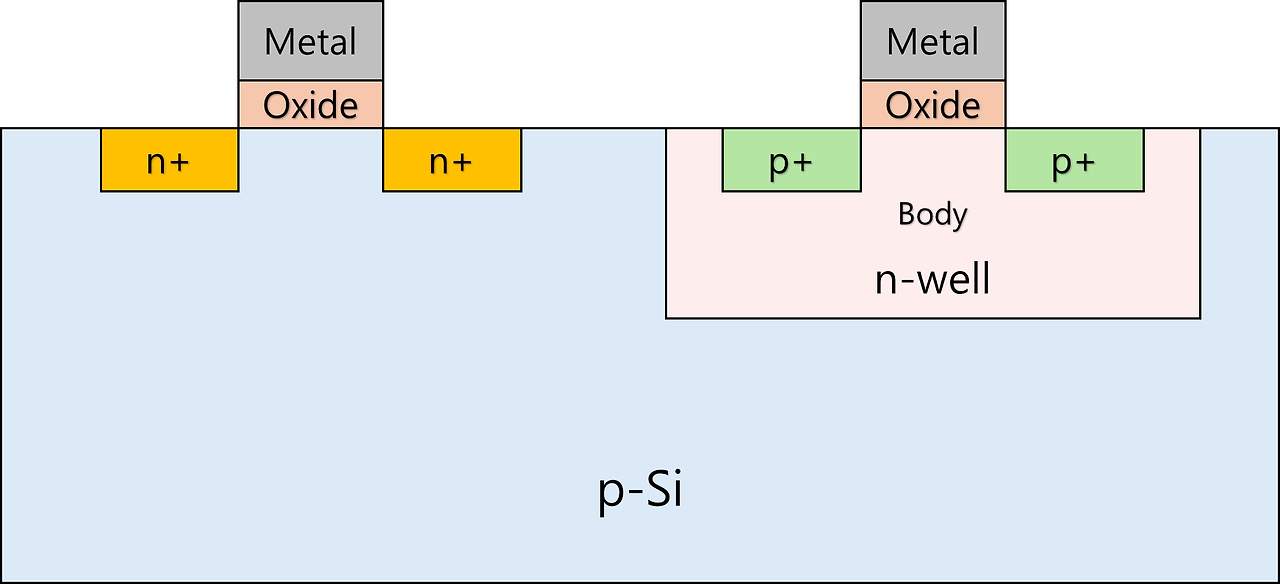

- single well 공정: n-si 또는 p-si body에 한 쪽에만 well을 만드는 공정

좌: n-well 공정 / 우: p-well 공정 - twin well 공정: 도핑되어 있지 않은 body의 양 쪽에 well을 만드는 공정

2. Well과 Substrate Tap

- Substarte tap: p substrate과 왼쪽의 p+ 연결 -> GND로 연결

- Well tap: n well과 n+ 연결 -> Vdd로 연결

3. Inverter Mask Set

- NMOS의 Width와 PMOS의 Width가 2배 차이나야 하는 이유: 이동도가 전자가 정공의 2배이므로, PMOS의 저항이 2배 -> W를 두배로 늘려주어 저항 동일하도록

Stick Diagram

- Stick Diagram 그리는 순서

- Path가 nMOS, pMOS 모두를 만족하도록 설정

- 모든 TR을 반드시 1회씨만 경유하도록 Path 설정

- Ex1) input이 A, B, C인 NAND

- CMOS Schematic 수행

- 위 두 조건에 만족하는 Path인 C - B - A 선정3. VDD PMOS NMOS GND순으로 가로선을 그리고, Path 순서대로 세로선 그리기

- CMOS Schematic에서 각 소자의 양단의 상태 표시

- 위 그림을 참조하면 A 양쪽에 VDD와 F, B와 A 사이에 VDD, B의 반대편에 F 등 각 소자 양단의 상태 표기 가능

- 같은 상태끼리 이어주면 완성

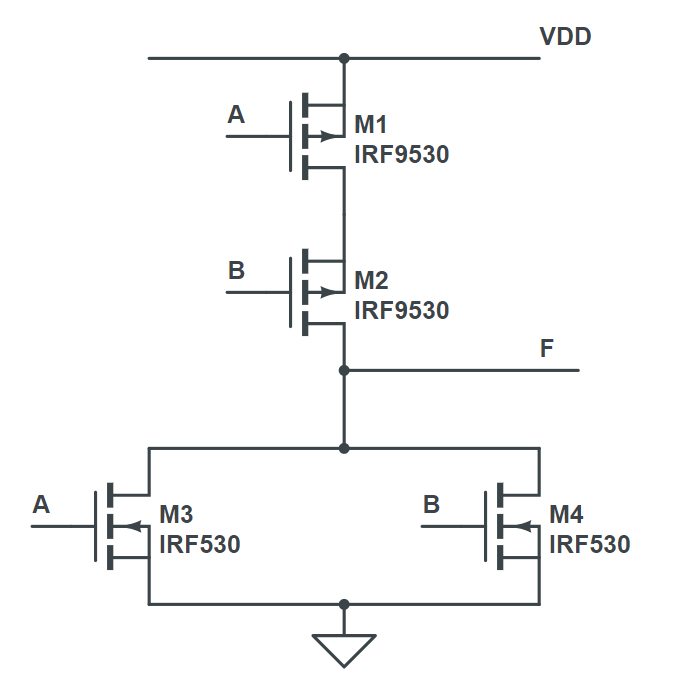

- CMOS Schematic 수행

- Ex2) Input이 A, B인 NOR

- CMOS Schematic 수행

- Path를 A - B로 설정 후 선 그리기

- CMOS Schematic에서 각 소자 양단의 상태 표시

- Stick Diagram에 상태 표시

- 같은 상태끼리 이어 Schematic 완성

- CMOS Schematic 수행

- Ex3) F = ~(A*B+C)

- CMOS Schematic 수행

- Path를 C - B - A로 설정 후 선 그리기

- CMOS Schematic에서 각 소자 양단에 상태 표시

- Stick Diagram에 상태 표시

- 같은 상태끼리 이어 Schematc 완성

- CMOS Schematic 수행