728x90

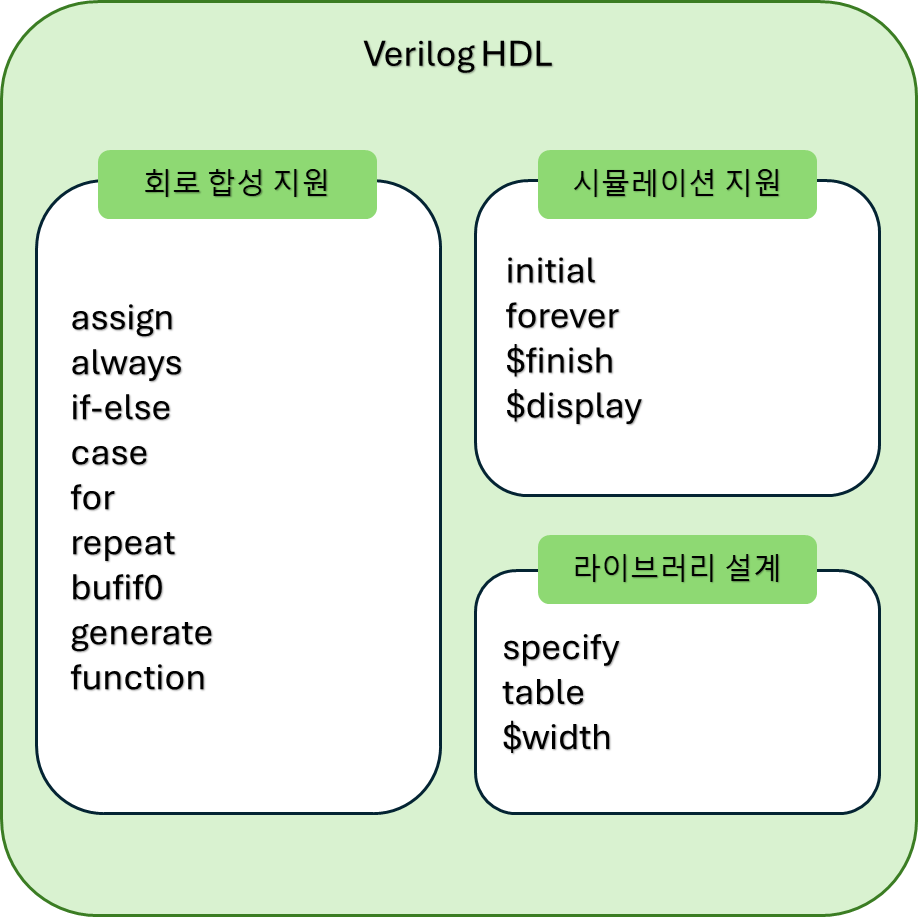

Verilog HDL 구문의 구성

- 회로 합성용 구문: 회로 합성 툴에서 게이트 수준 합성을 지원하는 구문

- 시뮬레이션용 구문: 시뮬레이션을 위한 테스트벤치의 작성에 사용되며, 회로 합성이 지원되지 않는다.

- 라이브러리 설계용 구문: 회로 합성에 적용되는 셀 라이브러리 설계에 사용되며, 셀의 기능, 지연, 핀 정보 등을 정의하는 데 사용된다.

Verilog HDL 모듈

- 모듈: Verilog HDL의 기본 단위

- Verilog HDL의 모듈 구성

module module_name (port_list); //머리부 //선언부 port 선언 reg 선언 wire 선언 parameter 선언 //몸체부 하위모듈 인스턴스 게이트 프리미티브 always 문 initial 문 assign 문 function, task 정의 function, task 호출 endmodule

- 머리부

- 키워드 module로 시작하여 모듈 이름, 포트 목록으로 구성되며 세미콜론(;)으로 끝남

- 키워드와 동일한 이름은 사용 불가, 가독성을 위해 밑줄이 포함될 수 있다.

- 모듈의 기능을 함축적으로 나타내는 모듈 이름을 사용하는 것이 좋다.

- 모듈 이름 다음의 괄호에는 모듈의 입출력 포트가 나열된다.

- 모듈의 포트 목록은 테스트벤치 모듈에서 생략 가능하다. - 선언부

- 입출력 포트 선언, 자료형 및 parameter 등의 선언이 이루어진다. - 몸체부

- 회로의 기능, 동작, 구조 등을 표현하는 Verilog HDL 구문들을 적절히 사용하여 회로의 기능과 구조를 모델링한다.

- Verilog HDL의 문장은 기본적으로 병행문이므로 문장의 순서에 무관하게 동일한 결과를 갖는다.

- 머리부

테스트벤치 모듈

- 테스트벤치(testbench): Verilog HDL로 회로 모델링 완료 후에는 Verilog HDL 소스코드에 대한 시뮬레이션을 통해 회로의 기능과 동작 타이밍을 검증해야 하는데, 이를 위한 Verilog HDL모듈을 테스트벤치라고 한다.

- 테스트벤치 모듈의 구조는 회로 모델링 모듈과 동일한 구조를 가지며, 머리부의 포트 목록은 생략한다.

- reg 변수 선언, 시뮬레이션되는 모듈의 인스턴스, 시뮬레이션 입력을 생성하는 initial/always 구문으로 구성된다.

- 일반적으로 시뮬레이션 입력은 initial 또는 always로 생성되므로 모두 reg 변수로 선언되어야 한다.

728x90

'자습시간 > Verilog' 카테고리의 다른 글

| UART 설계(1) - Baud Rate Generator 설계 (0) | 2024.07.22 |

|---|---|

| Verilog 자료형 (0) | 2024.07.13 |

| Verilog HDL의 어휘 토큰과 규칙 (1) | 2024.06.30 |

| Verilog HDL 개요 - HDL 기반 시스템 반도체 설계 과정 (1) | 2024.06.30 |