이번 게시글에서는 Digilent의 게시물과 IP 라이브러리를 통해 Pmod OLED의 데모 파일 구현을 진행합니다. 추후 이를 응용하여 Pmod OLED를 통해 다양한 기능을 구현할 예정입니다.

Vivado, Vitis 이용방법

Getting Started with Vivado and Vitis for Baremetal Software Projects - Digilent Reference

digilent.com

준비사항

- Vivado, Vitis 2023.2버전: 기존에 사용하던 2024.2버전으로는 호환이 되지 않아 해당 버전으로 수행했습니다.

- Digilent 보드 파일 다운로드

아래의 파일을 다운로드 받아 압축을 해제한 뒤,

\vivado-boards-master\vivado-boards-master\new\board_files 내의 모든 폴더를 다음의 경로에 복사합니다C:\Xilinx\Vivado\2023.2\data\xhub\boards\XilinxBoardStore\boards

- Vivado Library 다운로드(Pmod IP 사용 시 필요)

GitHub - Digilent/vivado-library

Contribute to Digilent/vivado-library development by creating an account on GitHub.

github.com

- Board Master XDC

GitHub - Digilent/digilent-xdc: A collection of Master XDC files for Digilent FPGA and Zynq boards.

A collection of Master XDC files for Digilent FPGA and Zynq boards. - GitHub - Digilent/digilent-xdc: A collection of Master XDC files for Digilent FPGA and Zynq boards.

github.com

Vivado

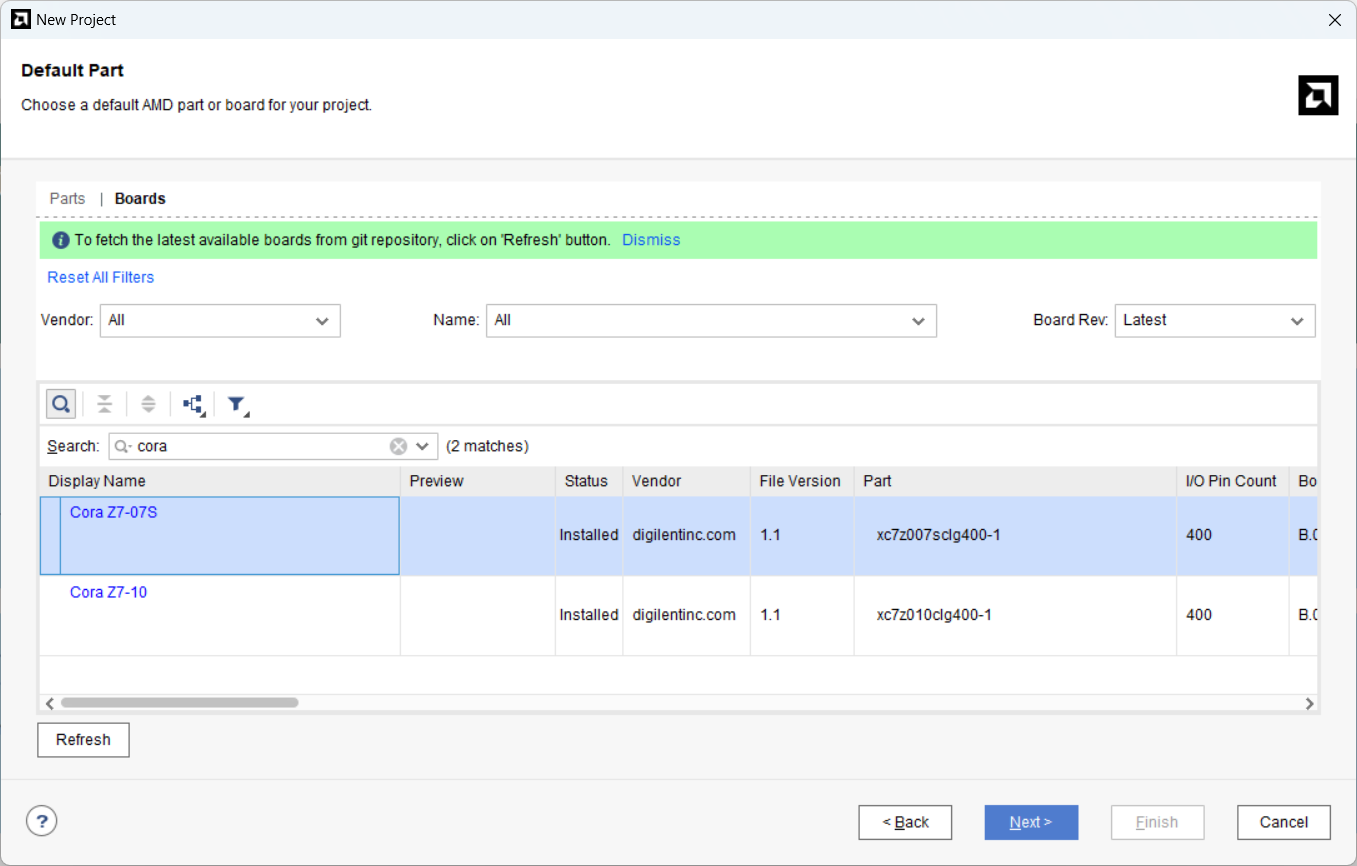

Vivado를 실행한 뒤, Create Project - Project Name 입력 - RTL Project(Do not specify source at this time) - 상단의 Boards 탭 선택 후 사용 보드 클릭 - Finish

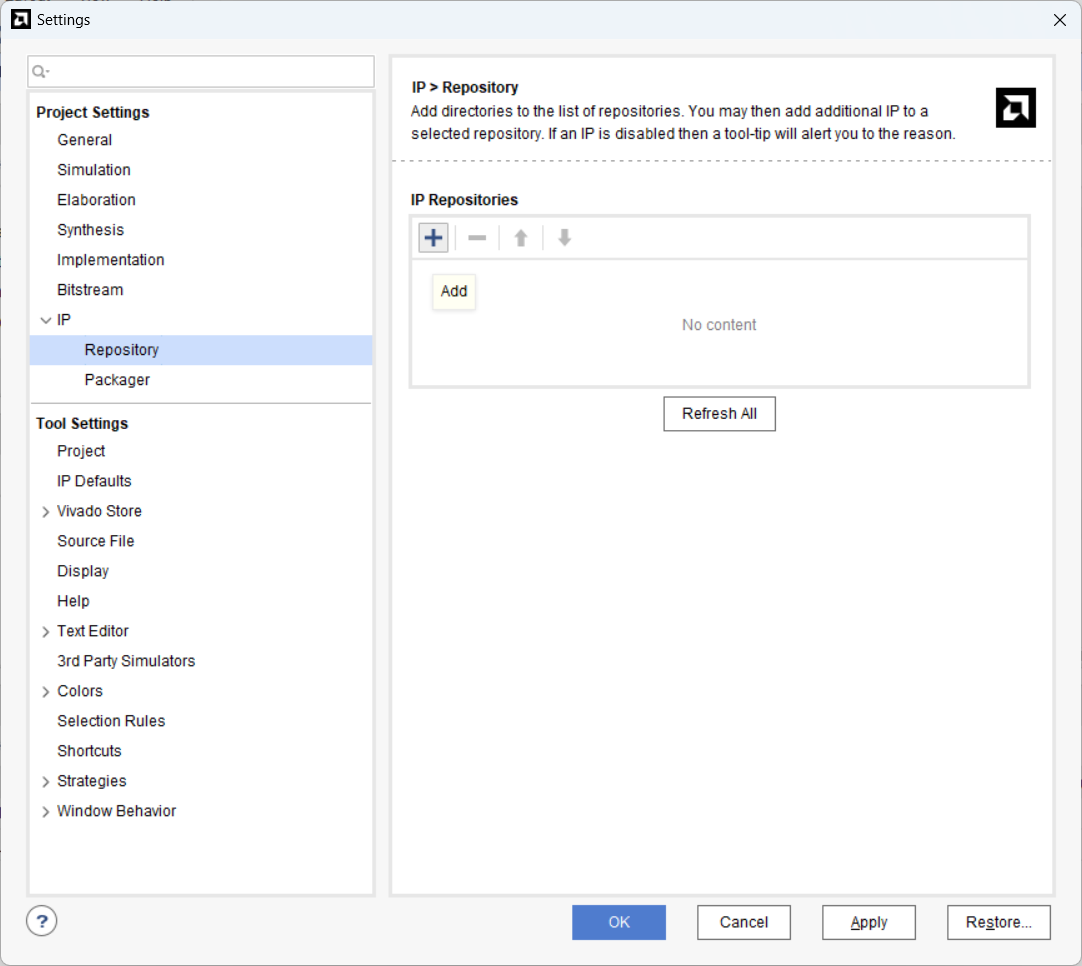

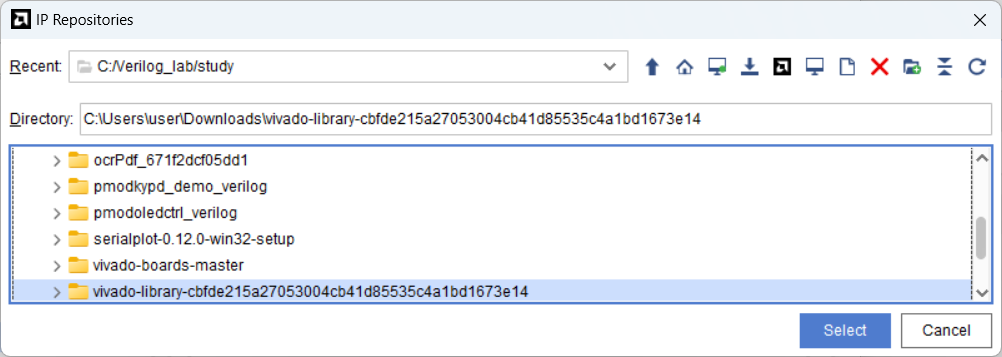

좌측 Project Manager 하단 Settings - IP - Repository에서 +버튼 클릭하여 vivado library 선택 - OK - OK

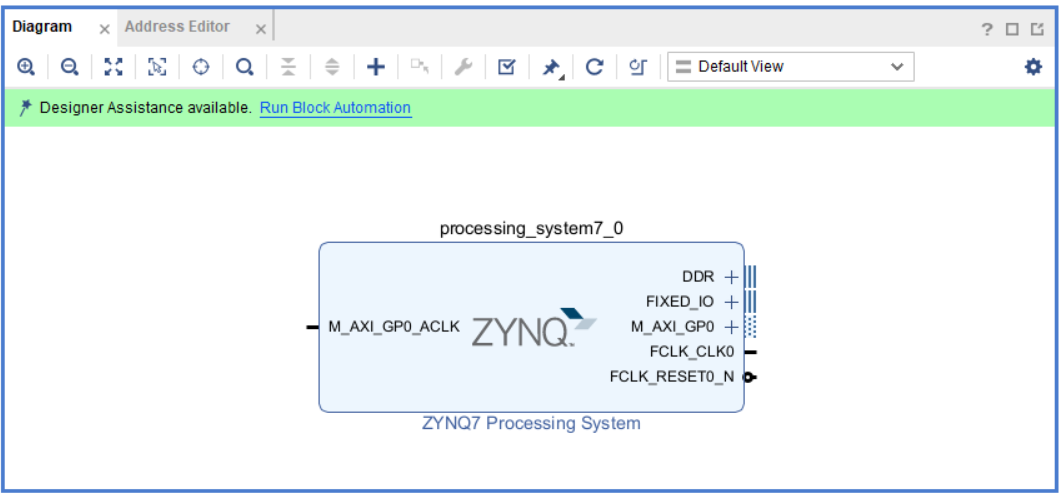

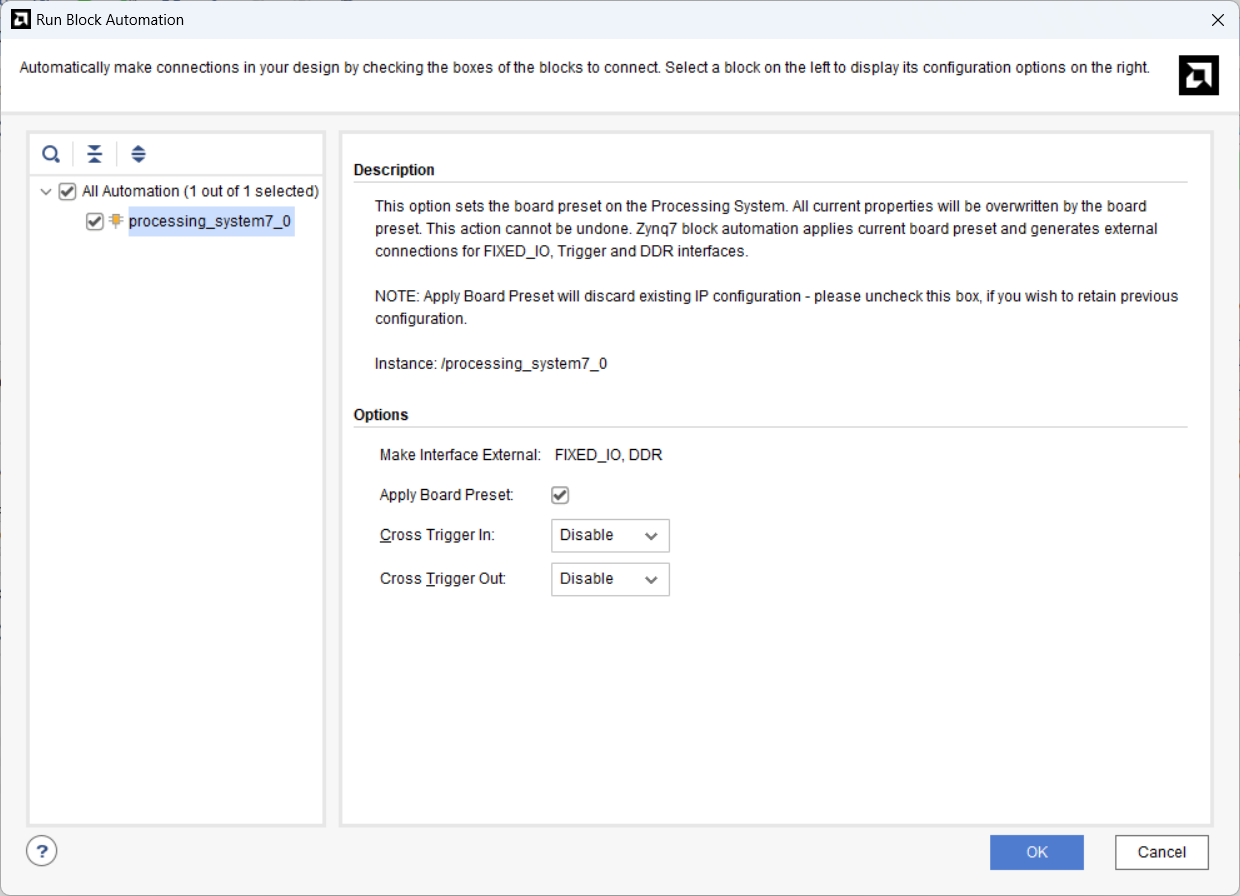

Create Block Design 후 Add IP(Ctrl + I)로 Zynq7 Processing Sytem(PS) 추가 - Run Block Automation

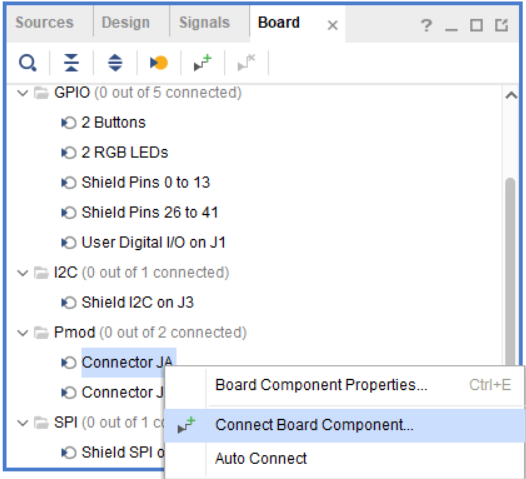

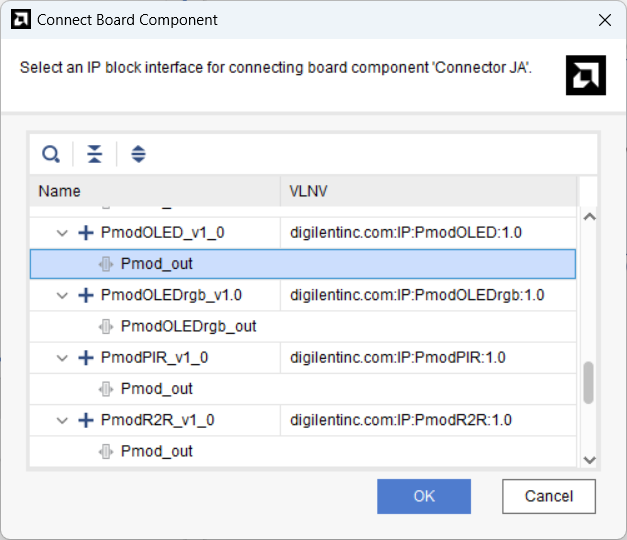

Board 탭에서 Connector JA 우클릭 - Connect Board Component 선택한 뒤 Pmod OLED를 선택합니다.

(JB 포트 사용하시면 해당 포트로 선택하시면 됩니다)

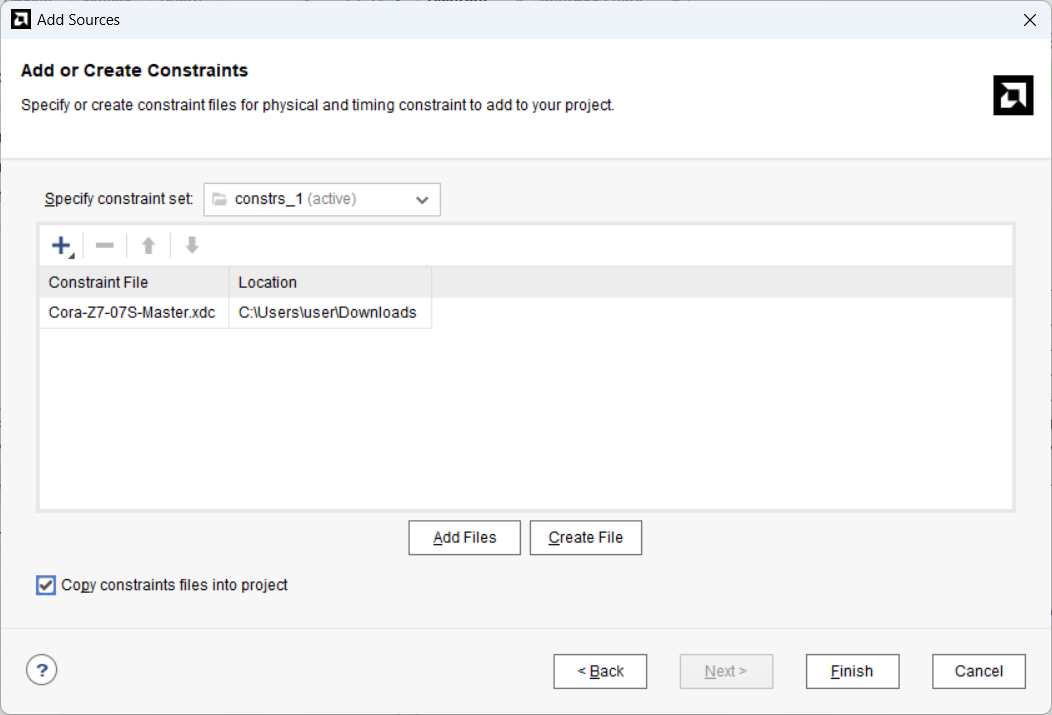

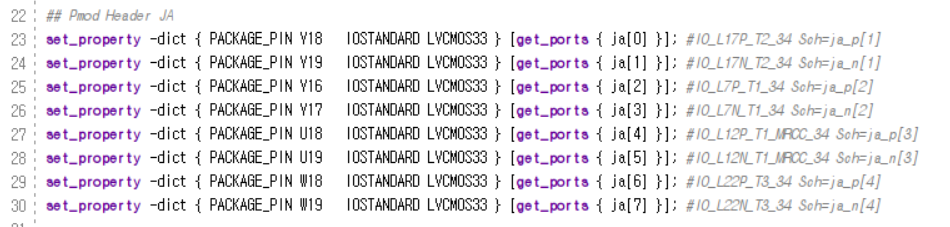

Sources - Add - Add or create constraints에서 Master.xdc 추가합니다.

방금 추가한 xdc파일을 열어 사용할 JA포트의 주석처리를 제거합니다.

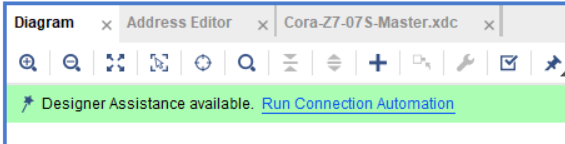

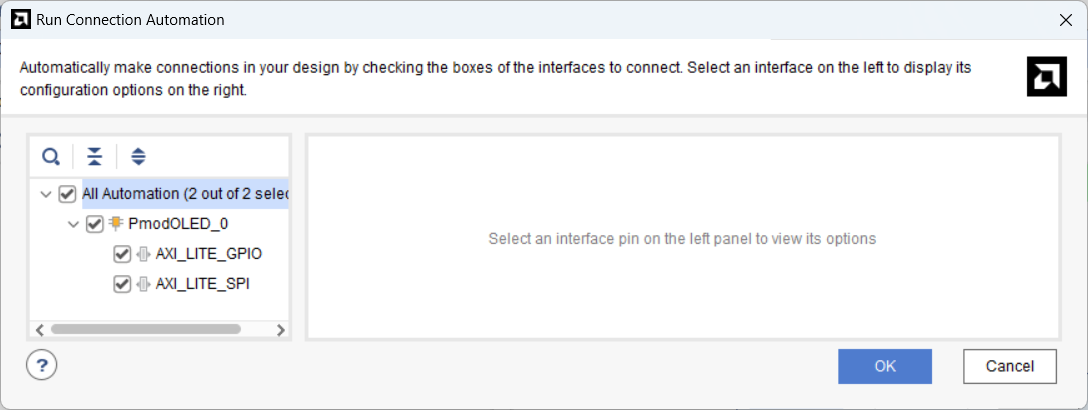

Diagram을 열어 Run Connection Automation을 수행합니다.

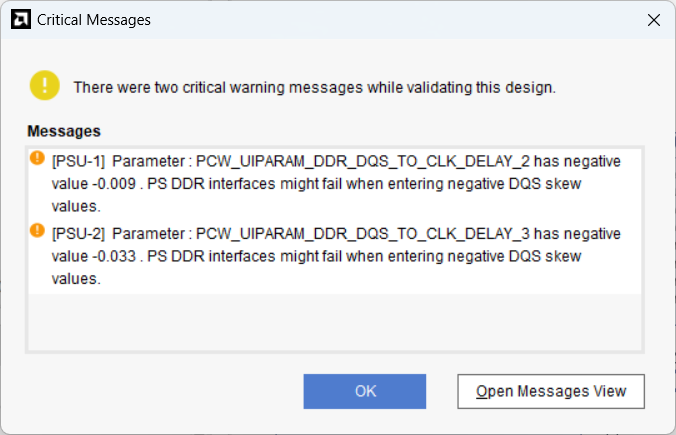

F6을 눌러 Validate Design을 수행합니다. 이 때 아래와 같이 PCW_UIPARAM_DDR_DQS_TO_CLK_DELAY 오류가 발생할 수 있으나 무시해도 됩니다. (대부분의 warnings와 일부 critical warnings는 무시 가능합니다.)

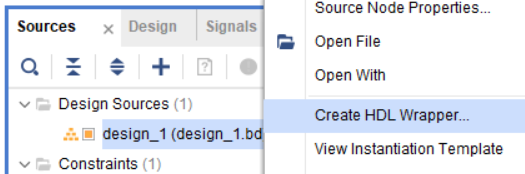

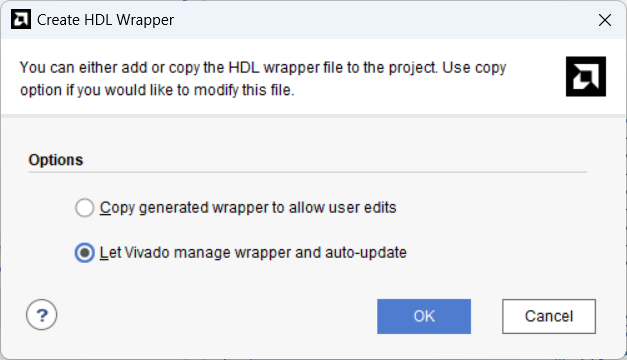

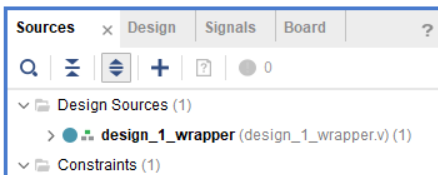

Sources 탭에서 Design Sources에 deseign_1.bd를 우클릭한 뒤 HDL Wrapper을 생성합니다.

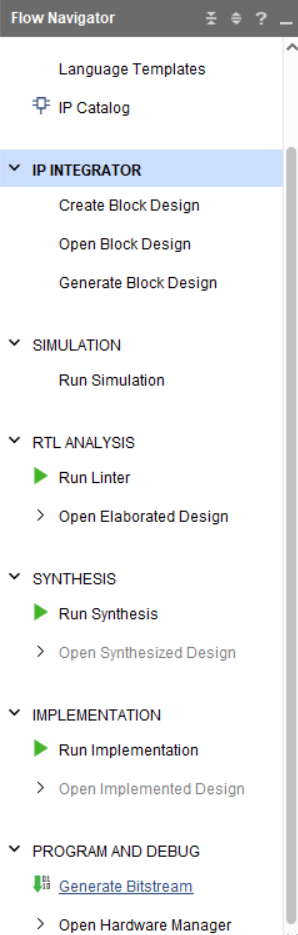

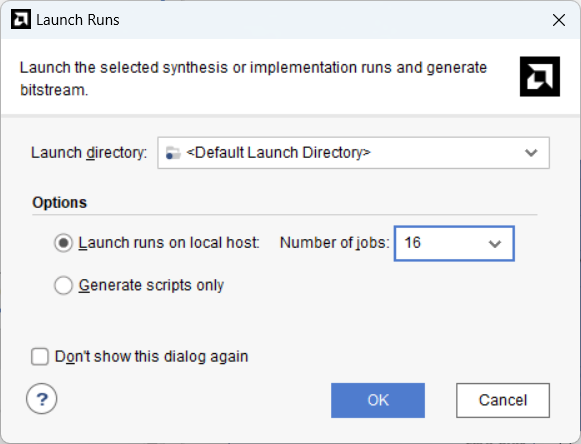

Wrapper 파일이 생성되었으면 Generate Bitstream을 수행합니다. 이 때 나타나는 Numbers of jobs는 컴퓨터의 리소스를 얼마나 빌드에 할당할 지 선택하는 옵션입니다. 가능한 경우 최댓값을 설정하는 것이 좋습니다.

- 다른 IP에 포함된 IP가 다른 보드 값(Board Value)과 함께 패키징되었다는 경고(Critical Warning)는 무시해도 됩니다.

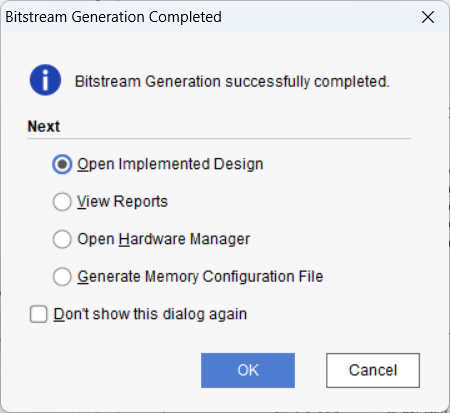

Bitstream 완료 후 선택 가능한 옵션은 다음과 같습니다.

- "Open Implemented Design" → 실제 구현된 하드웨어 디자인을 확인하고, FPGA 칩에 배치될 설계를 볼 수 있습니다.

- "View Reports" → FPGA 리소스 사용량 및 디자인 정보를 확인할 수 있습니다.

- "Open Hardware Manager" → Vivado의 하드웨어 매니저를 직접 실행하여 FPGA 보드에 하드웨어를 프로그래밍할 수 있습니다.

- 주로 소프트웨어가 포함되지 않은 하드웨어 전용 디자인에서 사용됩니다.

- "Generate Memory Configuration File" → FPGA 전용 디자인을 플래시 메모리에 저장하기 위한 파일을 생성할 수 있습니다.

원하는 옵션이 없다면 "Cancel"을 클릭하여 계속 진행합니다.

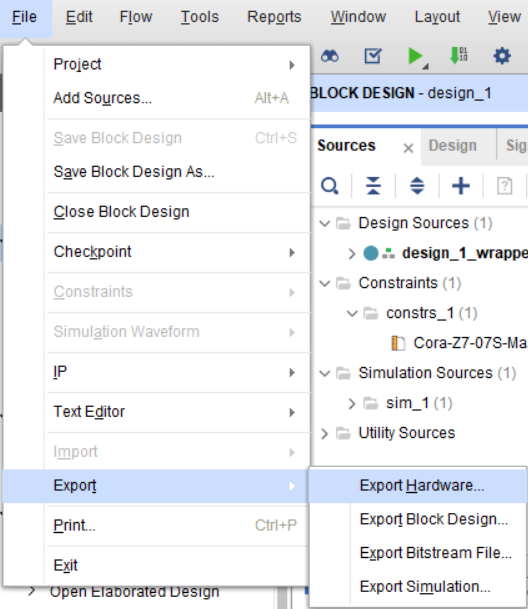

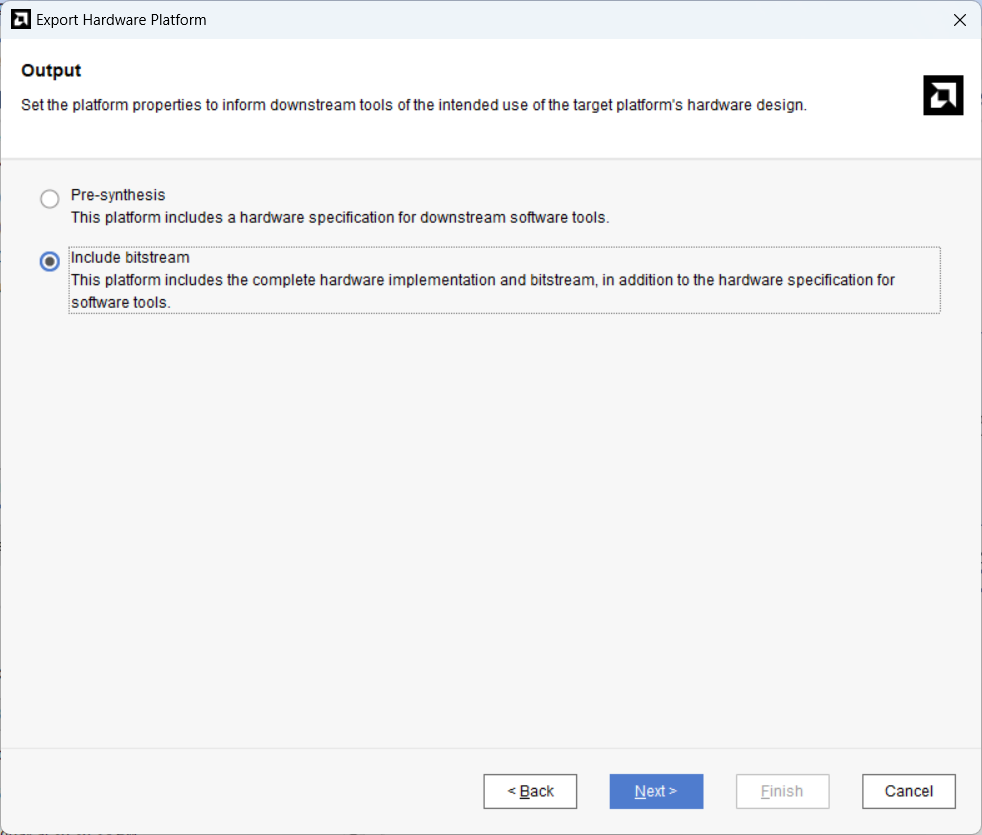

Bitstream 파일 생성이 완료되었으면 상단의 File 탭 - Export - Export Hardware 선택 후 Include Bitstream 옵션으로 XSA 파일을 내보냅니다.

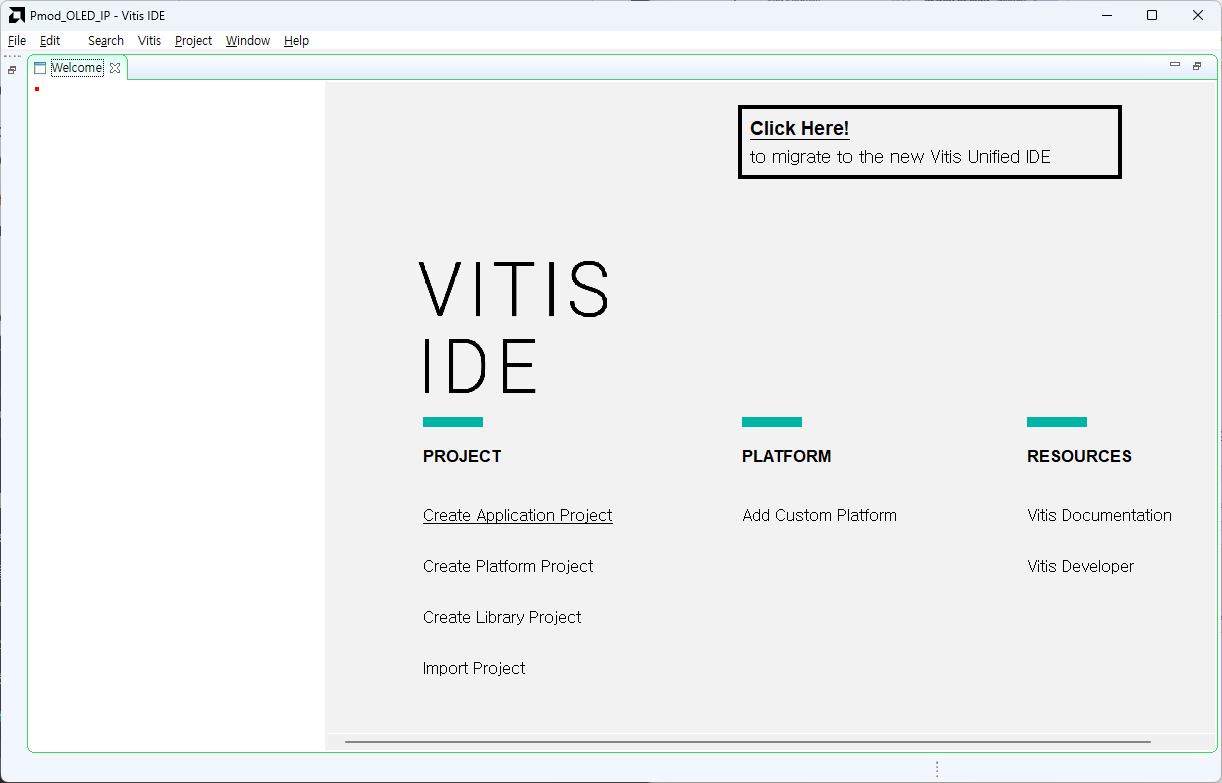

Vitis

XSA 파일을 내보낸 위치를 기억한 후 Vitis를 실행합니다.

- Vitis가 아닌 Vitis Classic을 실행합니다.

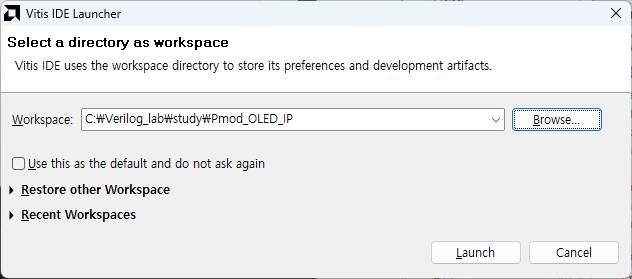

Vitis가 실행되면 Workspace를 설정하는데, 기존 vivado 프로젝트 폴더로 설정했습니다.

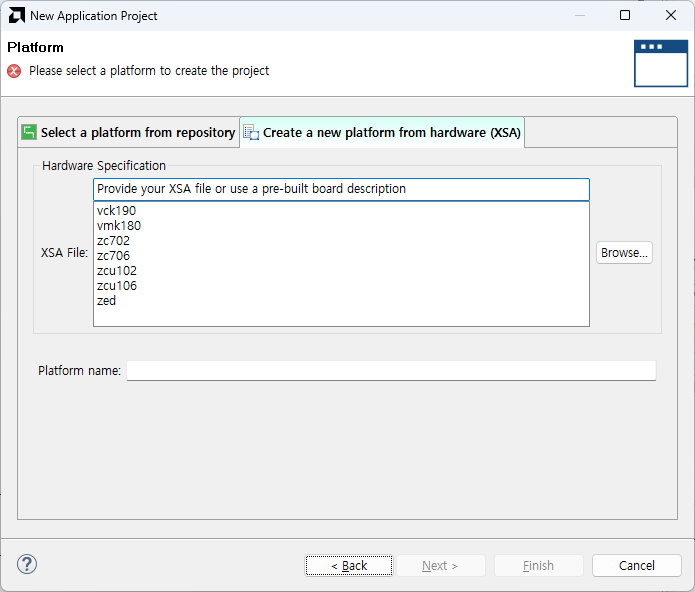

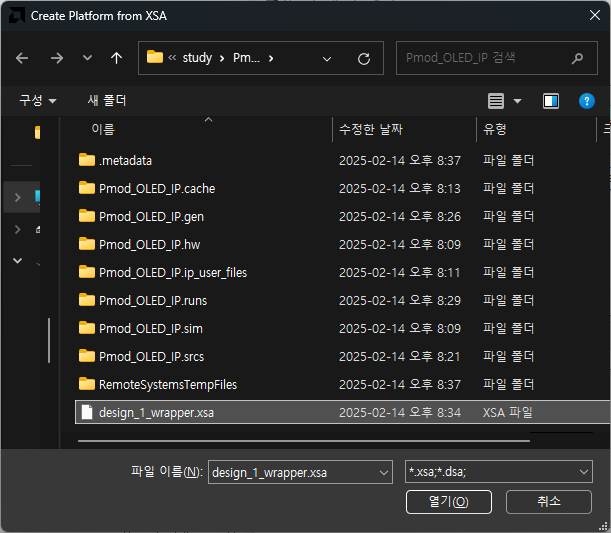

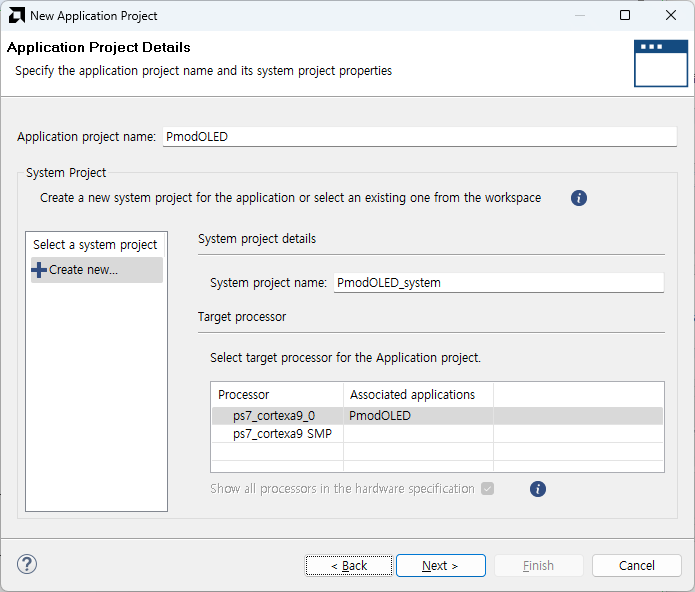

Create Application Project 선택 후 Next - 상단의 Create a new... 선택 후 Browse - 저장한 XSA 파일을 선택해줍니다.

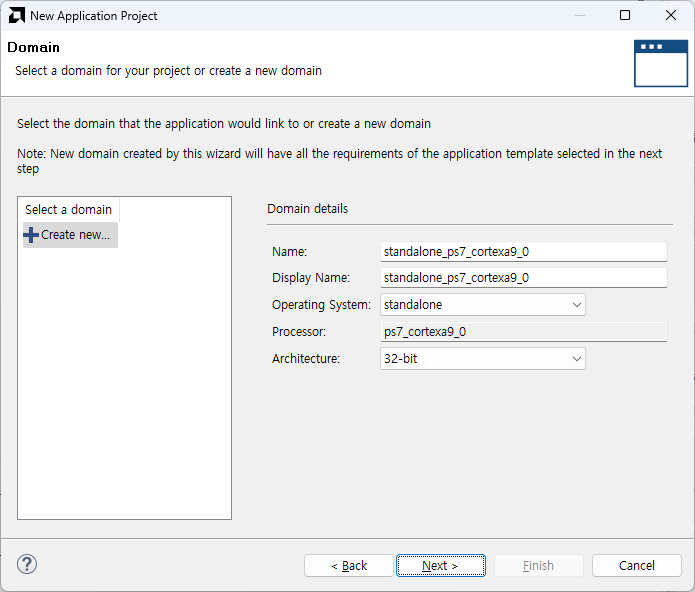

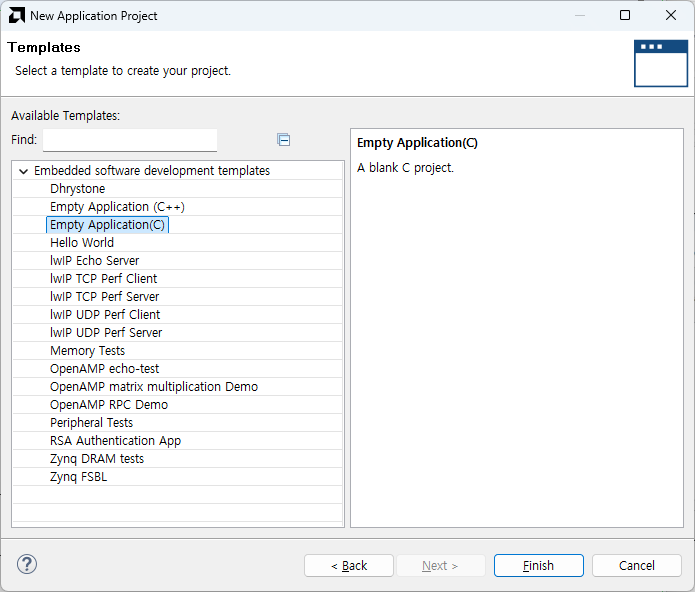

Next - Project 이름 설정 후 Next - Domain 설정은 건드리지 않고 Next - Empty Application(C) 선택 후 Finish를 눌러줍니다.

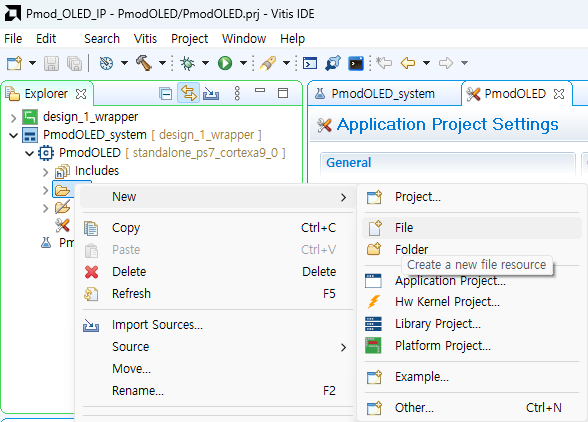

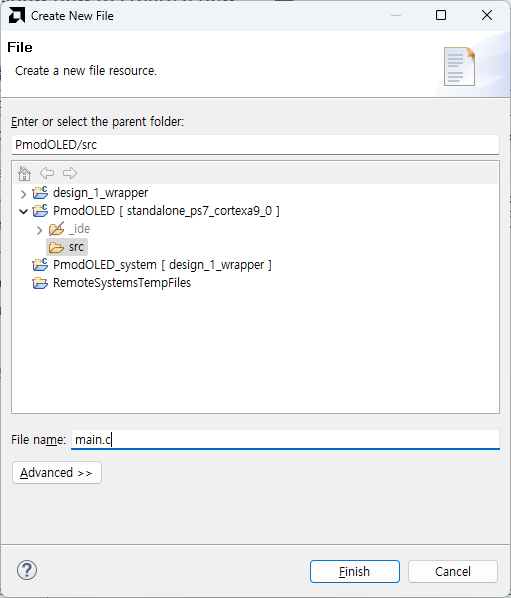

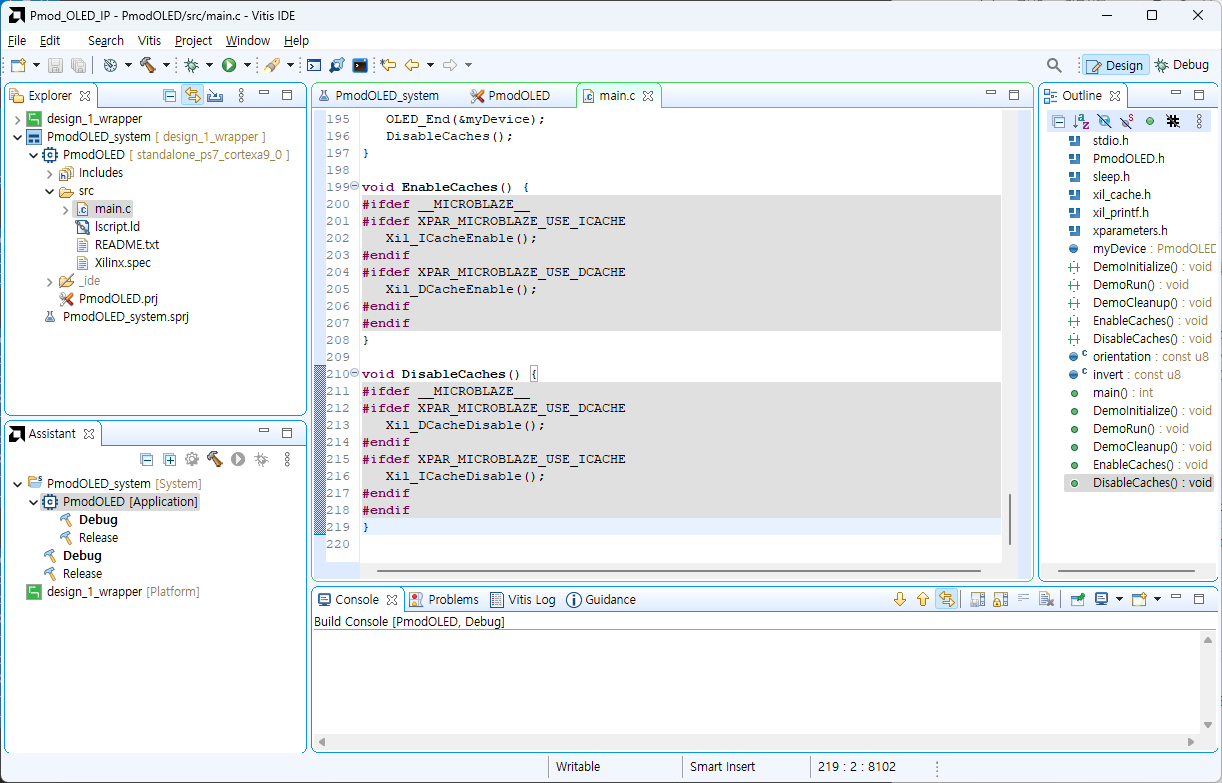

위 과정까지 완료되면 아래와 같은 창을 확인할 수 있습니다. 이제 src폴더를 우클릭해서 새 파일을 생성해주고, main.c로 이름을 지정합니다.

다운받았던 vivado library에서 PmodOLED 폴더를 찾아 main.c파일의 내용을 복사해서 vitis에 붙여넣기합니다.

main.c 위치: [\vivado-library-v2019.1-1\ip\Pmods\PmodOLED_v1_0\drivers\PmodOLED_v1_0\examples]

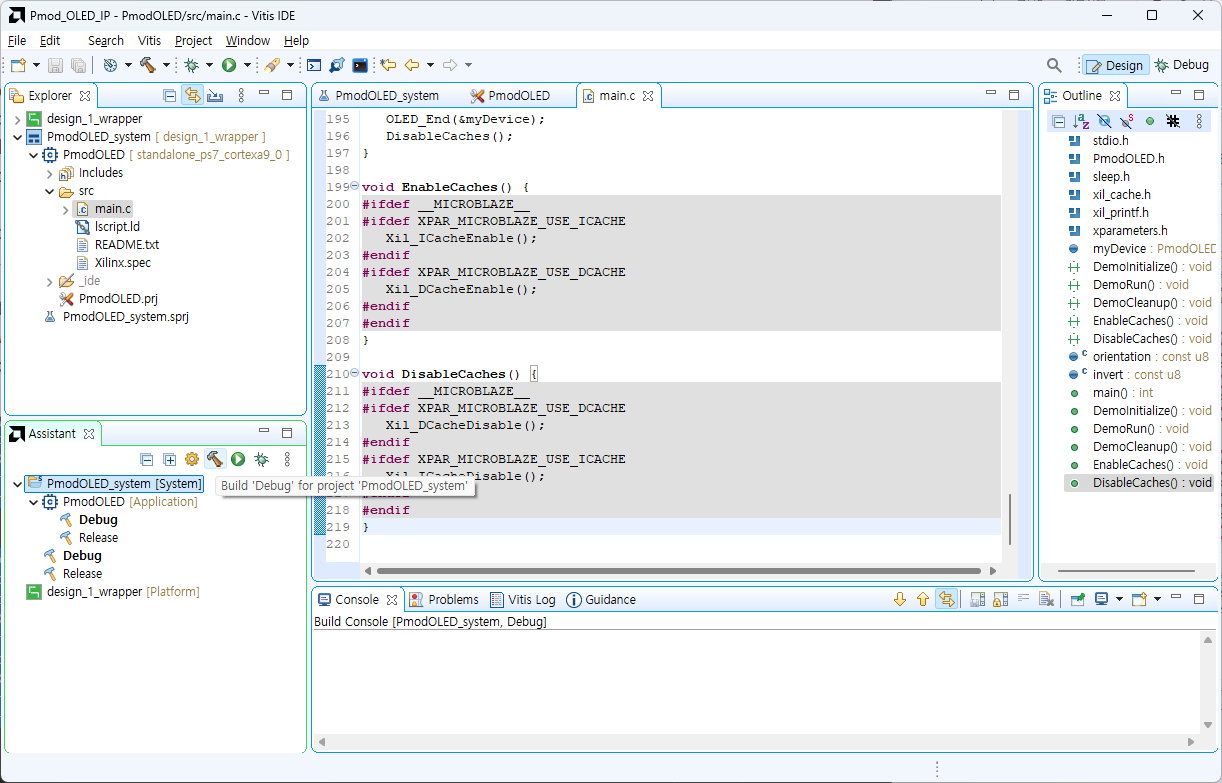

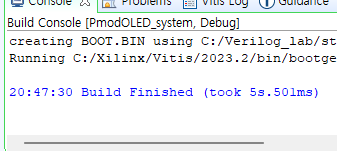

main.c를 저장한 뒤 좌측 하단에 system을 클릭하고 Build를 수행합니다.

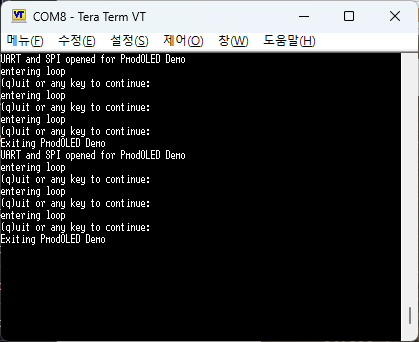

Build가 완료되면 TeraTerm을 실행시키고, 시리얼포트를 다음과 같이 설정합니다.

- Baud Rate 115200(MicroBlaze 보드는 9600)

- 데이터 8bit

- 패리티 none

- 스탑비트 1bit

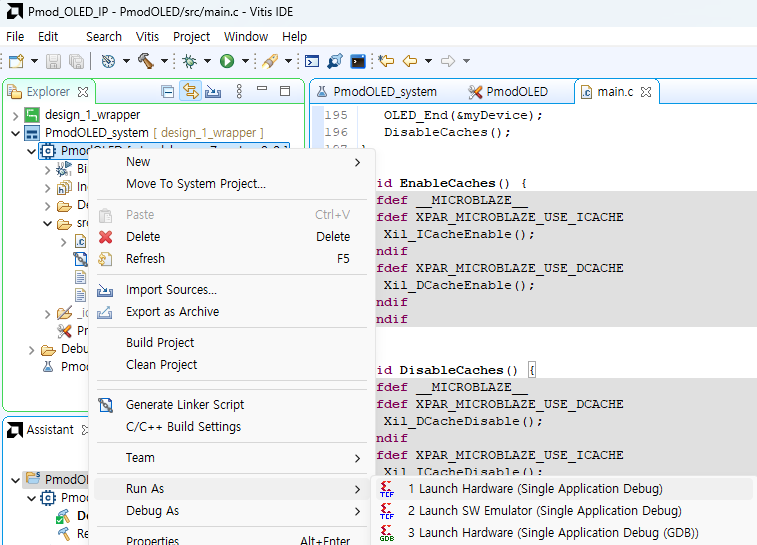

TeraTerm 설정이 완료되었으면 Vitis에서 Explorer 탭의 Application을 우클릭한 뒤 Run As - 1 Launch Hardware (Single Application Debug)를 선택합니다.

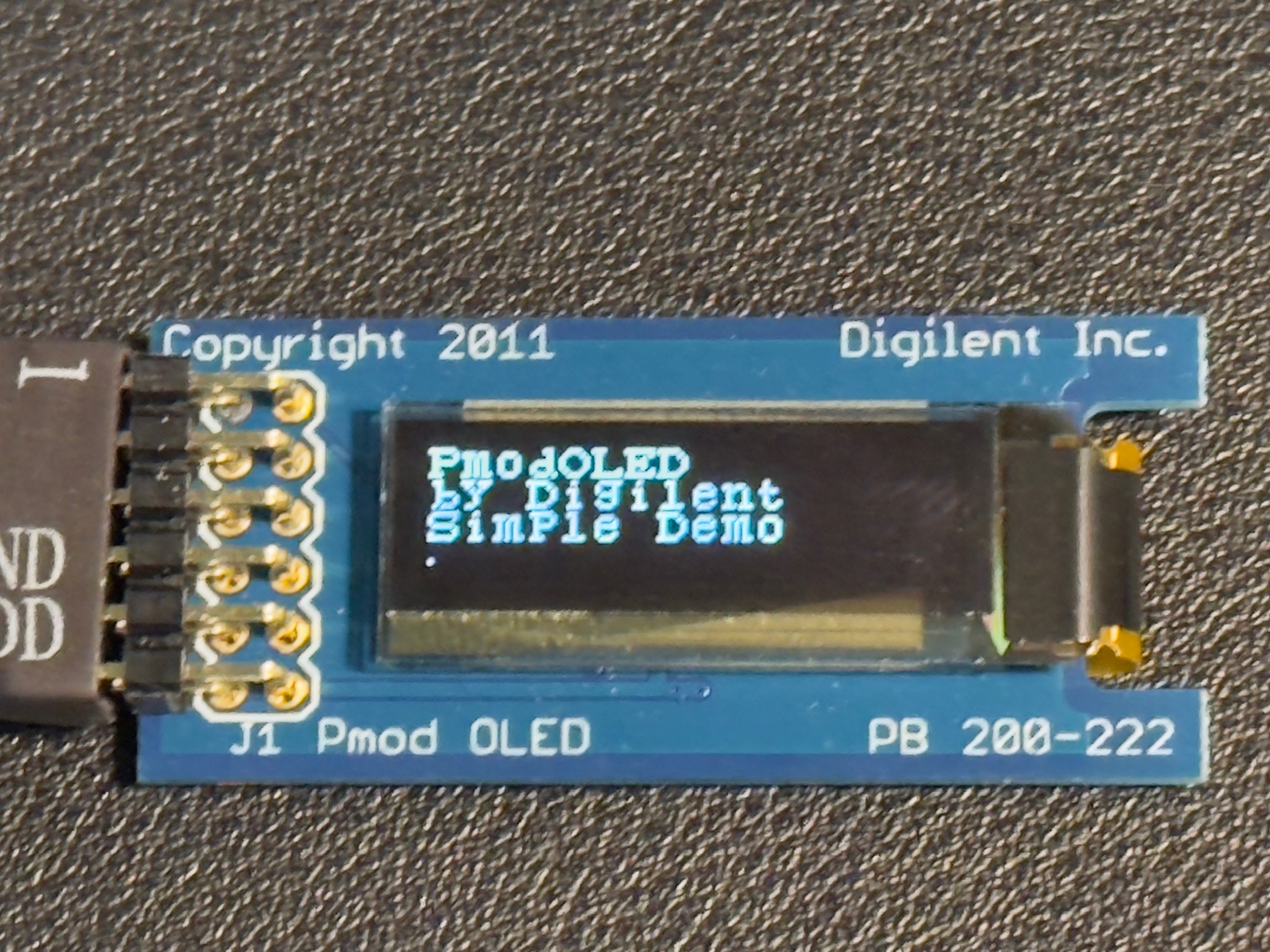

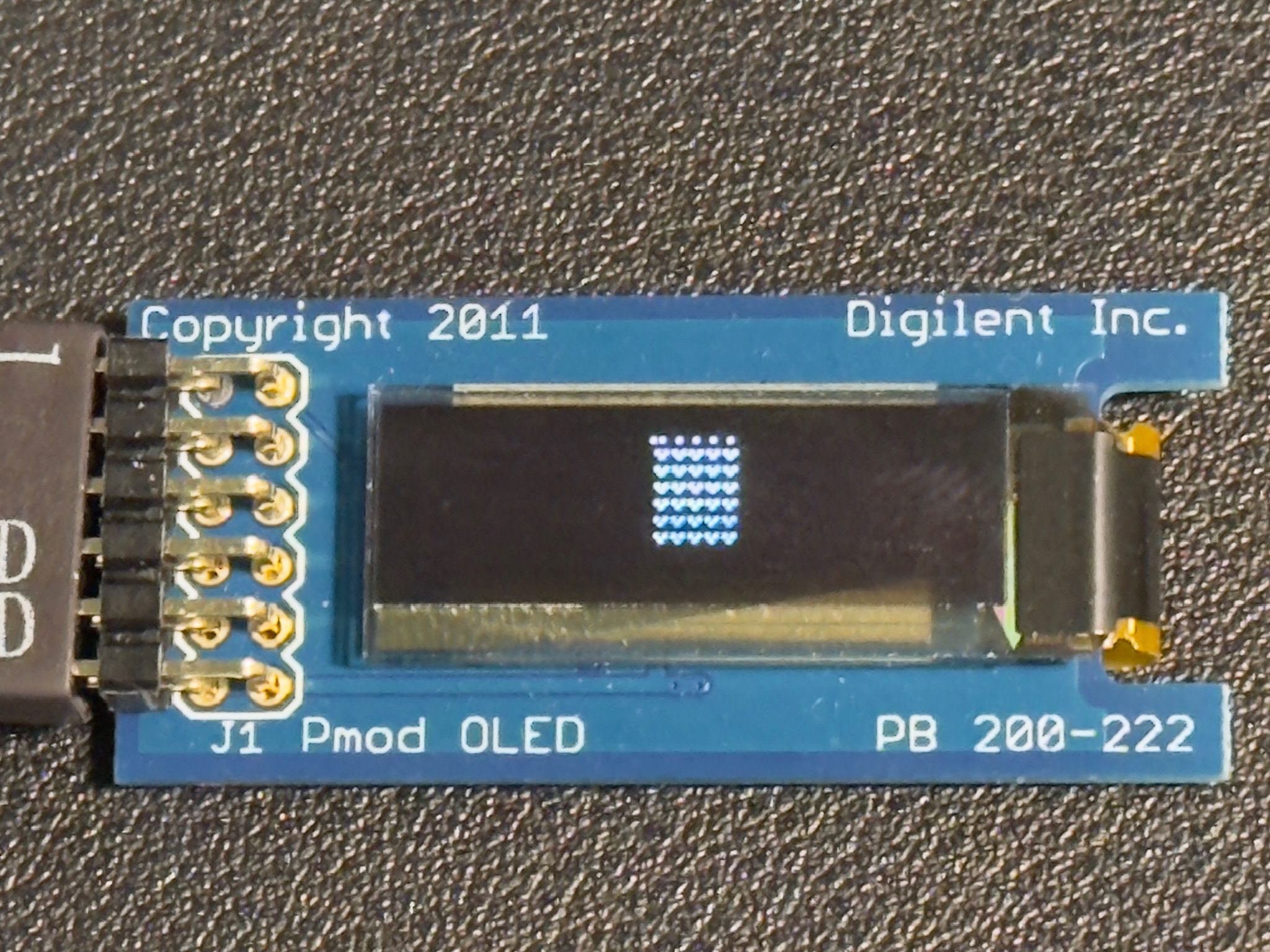

다음 두 개의 화면이 디스플레이되며, TeraTerm을 통해 다시 재생하거나 종료할 수 있습니다.

(Zynq 보드에서는 반드시 q를 눌러 종료해야 합니다.)

'자습시간 > Verilog' 카테고리의 다른 글

| Pmod OLED 공룡 게임 만들기(2) (0) | 2025.02.17 |

|---|---|

| Pmod OLED 공룡 게임 만들기(1) - 비트맵 이미지 구현 (0) | 2025.02.17 |

| Verilog 복습 프로젝트(3) - Decoder 설계 [Pmod KYPD 이용] (0) | 2025.02.12 |

| Verilog 복습 프로젝트(2) - 스탑워치 설계 (0) | 2025.02.12 |