1. Innovus Import Design 과정

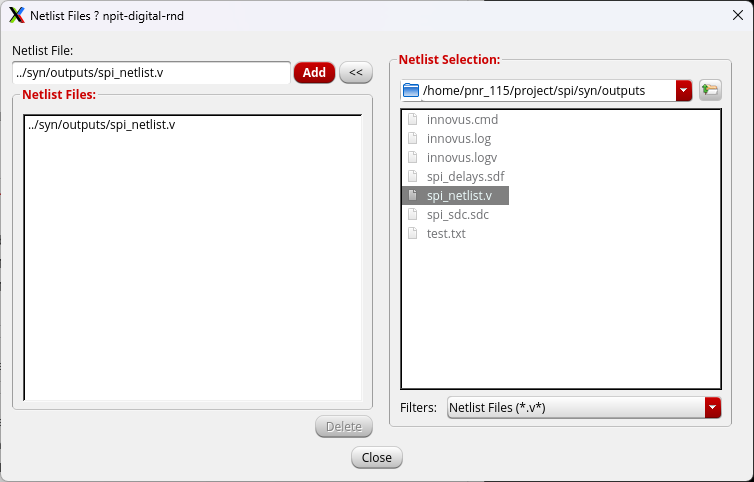

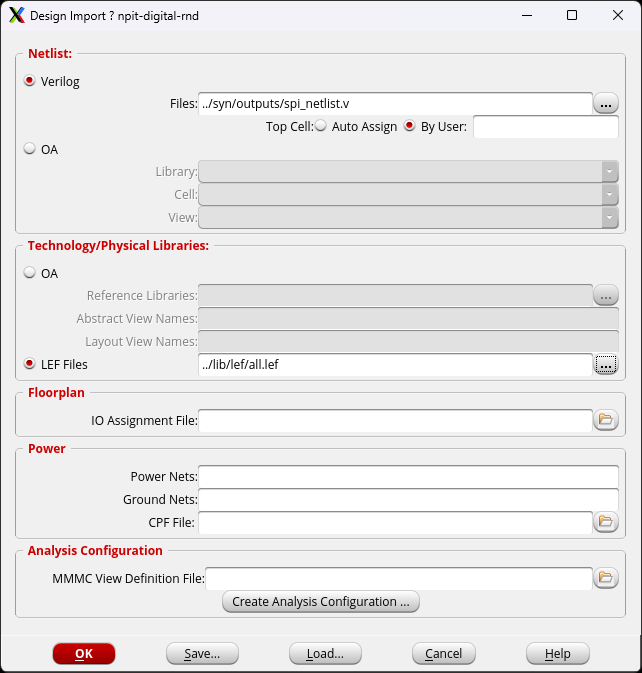

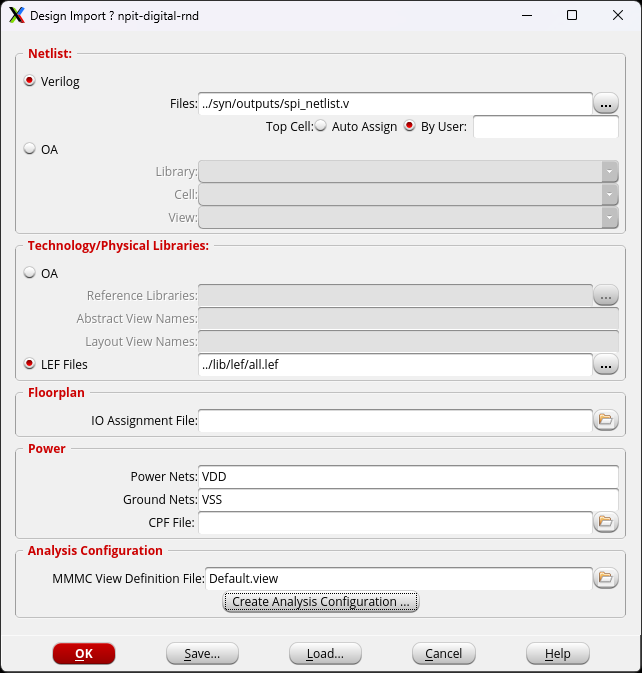

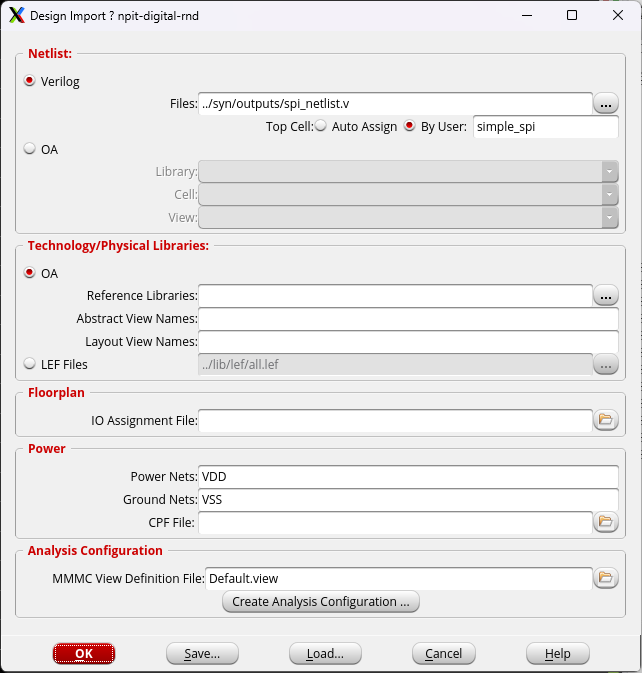

1. innovus 실행 후 File - import design - Verilog 에서 경로 설정하여 netlist 파일 추가

2. Techgnology/Physical libraries 탭에서 LEF Files 선택 후 경로 찾아 파일 추가

3. Power 탭의 Power nets와 Ground nets 설정

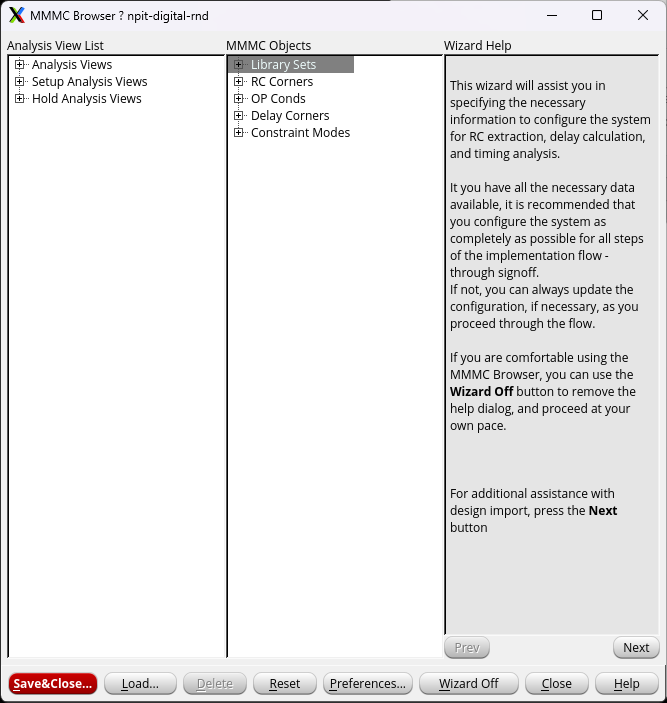

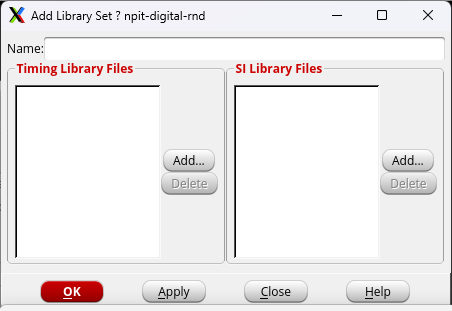

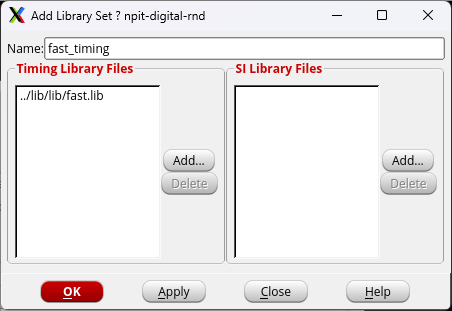

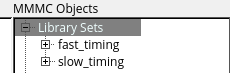

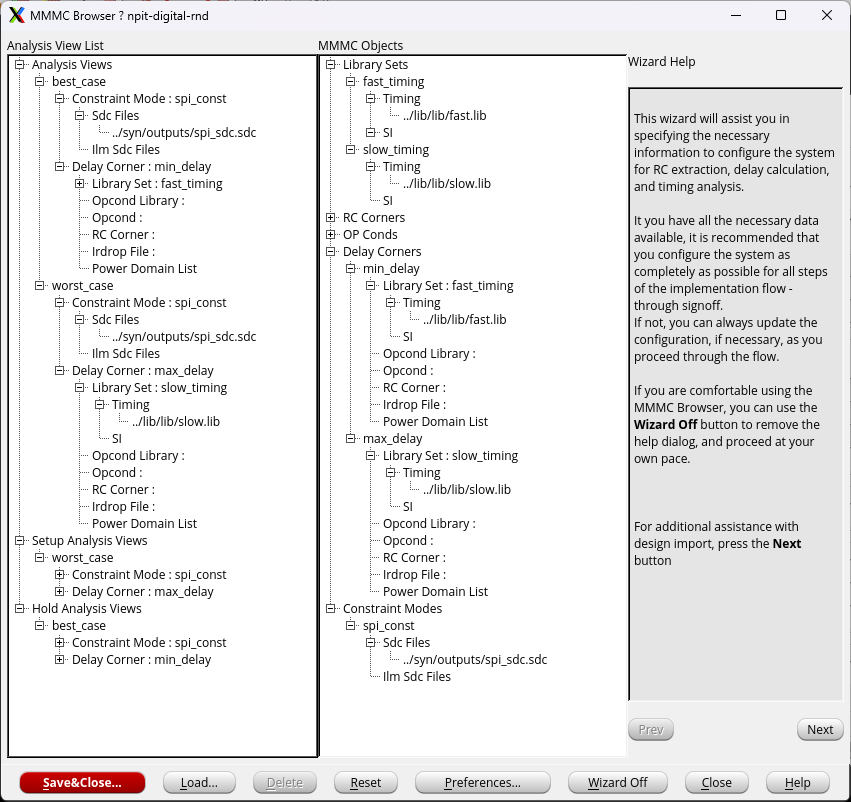

4. Analysis 탭의 Create~~눌러 실행 후 Library Sets 더블클릭 - Timing Library Fiiles의 Add 클릭 후 fast.lib 추가

- fast.lib은 타이밍이 빨라 올라가는 시간이 짧음 - 이름을 fast timing으로 설정

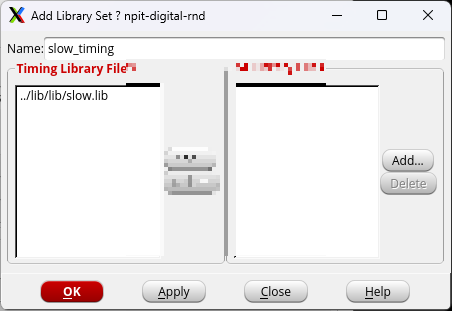

5. Library Sets 더블클릭 - Timing Library Fiiles의 Add 클릭 후 slow.lib 추가

- slow.lib은 타이밍이 느려 올라가는 시간이 길어짐 - 이름을 slow_iming으로 설정

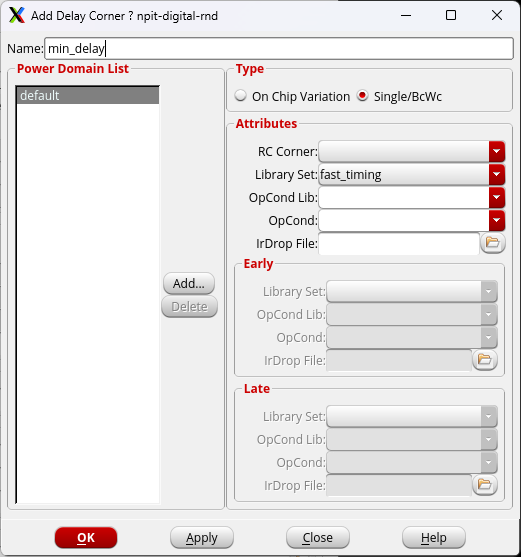

6. Delay Corners 더블클릭하여 실행 후 min_delay 로 이름 설정

- fast timing으로 실행 시 delay가 적어지므로 fast timing 사용

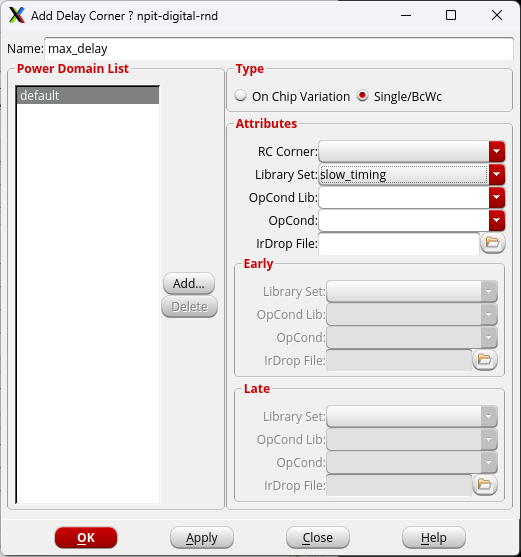

7.Delay Corners 더블클릭하여 실행 후 max_delay 로 이름 설정

- low timing으로 실행 시 delay가 길어지므로 slow timing 사용

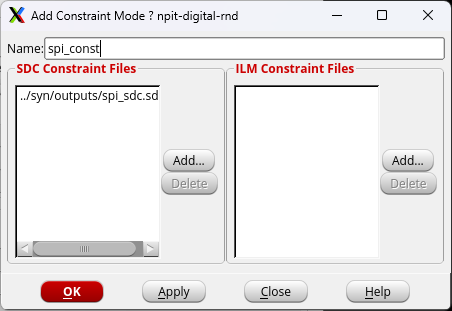

8. Constraint modes 더블클릭 후 파일과 이름 설정

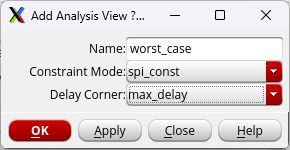

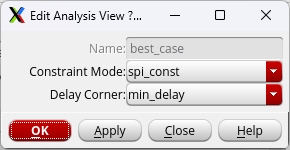

9. 좌측의 Analysis Views 더블클릭 후 설정

- min delay의 경우 동작 속도가 빨라지므로 best_case로 설정

- max delay의 경우 동작 속도가 느려지므로 worst_case로 설정

10. Setup과 Hold 설정

- Hold time

- Rising Edge 후 상태를 읽어들이는 데 필요한 최소 시간

- Holdtime이 커지면 Hold Time Violation이 발생하기 쉬워짐 -> Holdtime을 줄이기 위해 BestCase로 설정해야 유리

- Setup time

- Data를 읽어들이기 위해 switching이 발생하기 전까지 필요한 최소 유지 시간(FlipFlop이 준비할 시간)

- Setuptime이 작아지면 Setup Viloation이 발생하기 쉬워짐 -> Setuptime을 늘리기 위해 WorstCase로 설정해야 유리

11. Save & Close 후 Design Import 저장

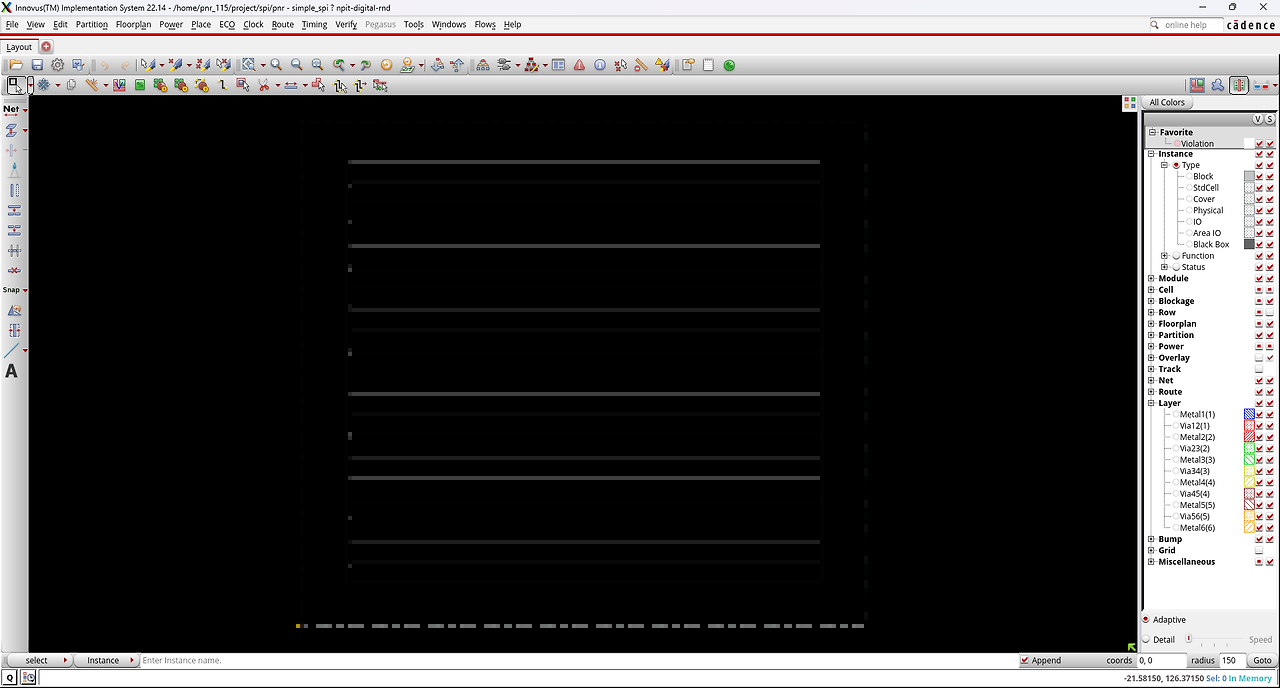

12. 저장 후 OK - 창 확인

2. Floor Plan

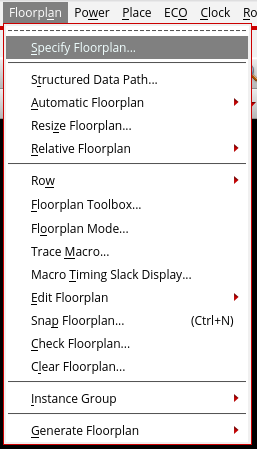

1. Floor Plan - Specify Floor Plan

- Cell과 Core 외에 빈 자리에 Routing을 위한 공간을 남기기 위해 Core Utilization을 0.7로 설정 -> 자동으로 값 변경됨

- Core Boundary로 사용하는 파트는 Core Margins by: 아래에서 적용

2. 적용 후 OK

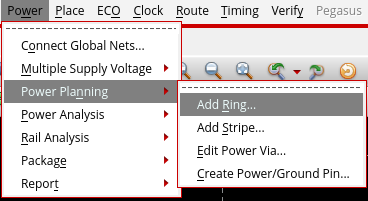

3. Power Planning & Power Routing

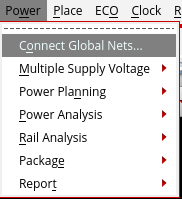

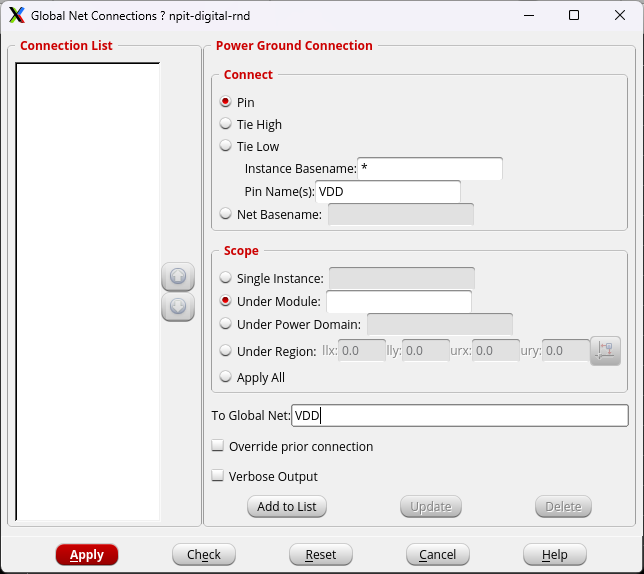

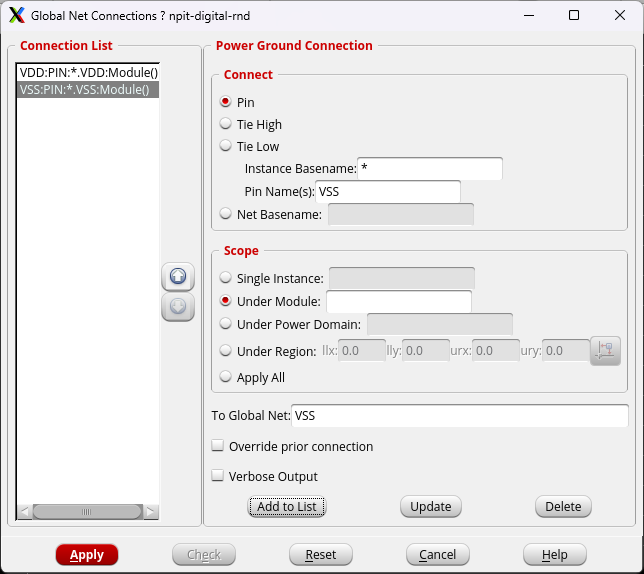

1. Connect Global nets를 실행하기 위해 Power- Connect Global Nets

2. VDD 와 VSS을 각각 Pin Name과 To Global Net에 모두 입력 후 Add to List

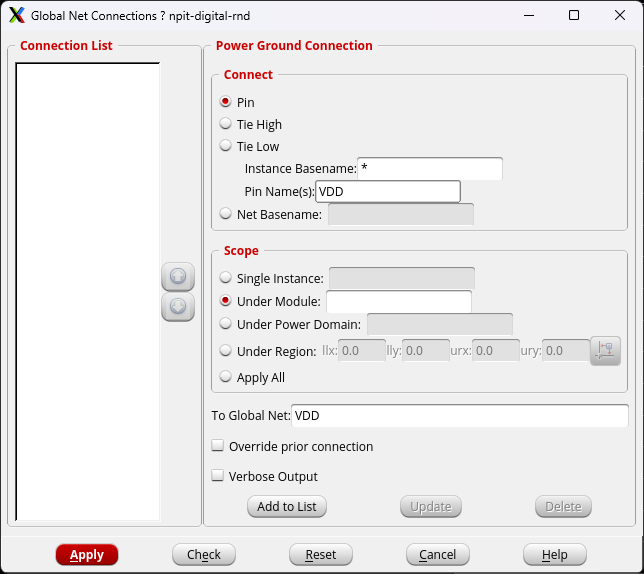

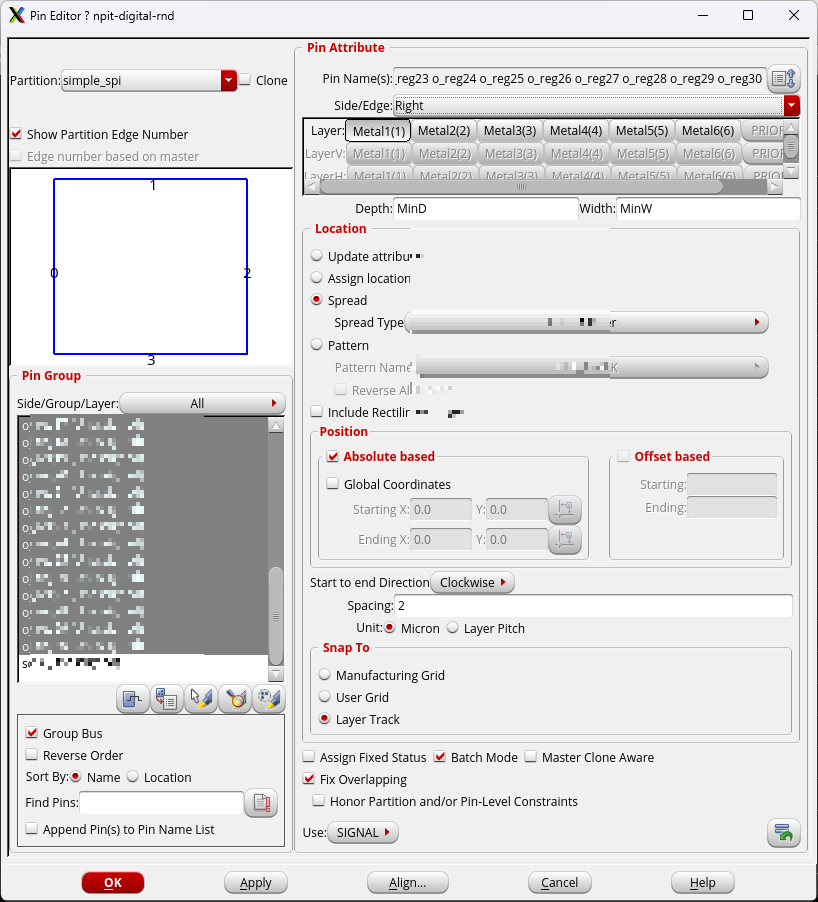

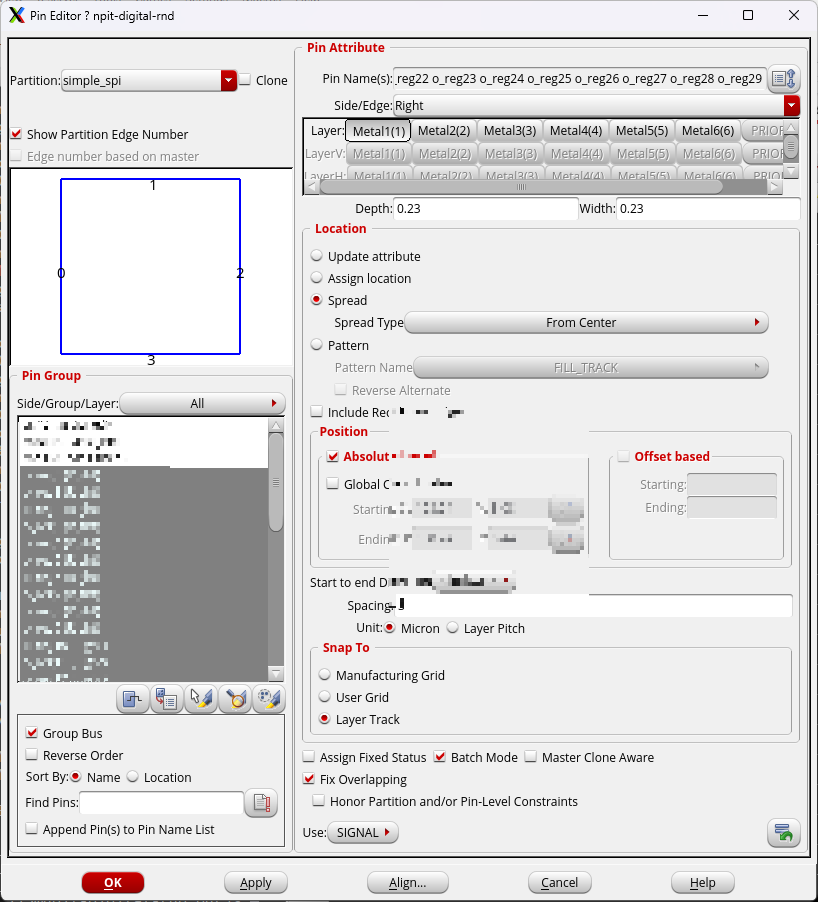

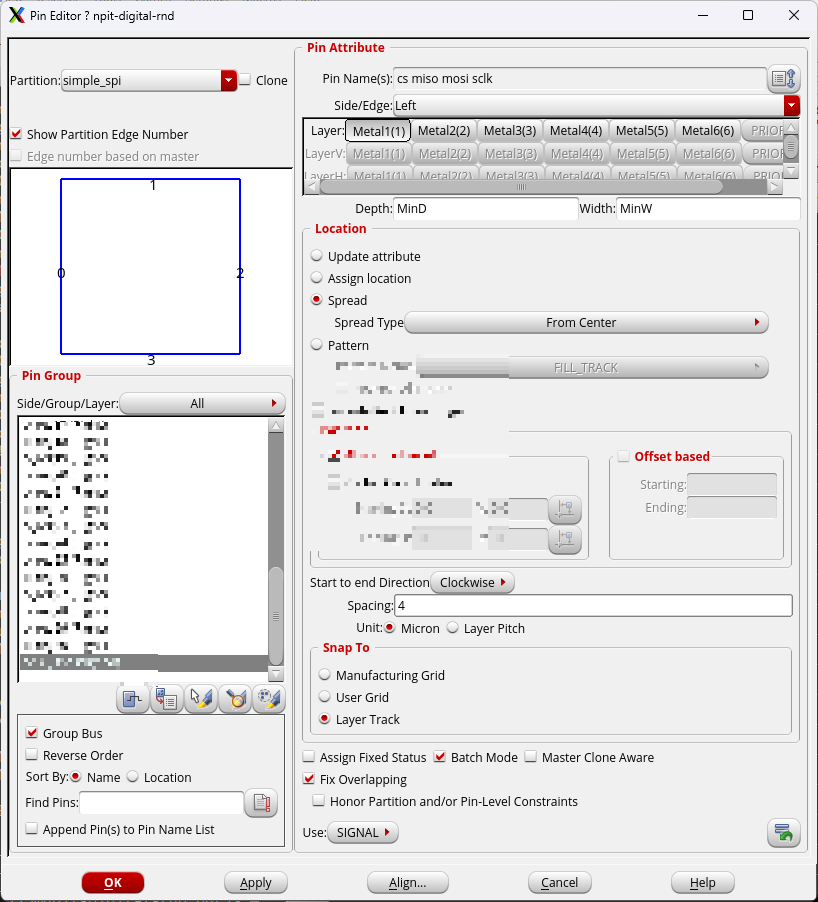

3. Edit - Pin Editor

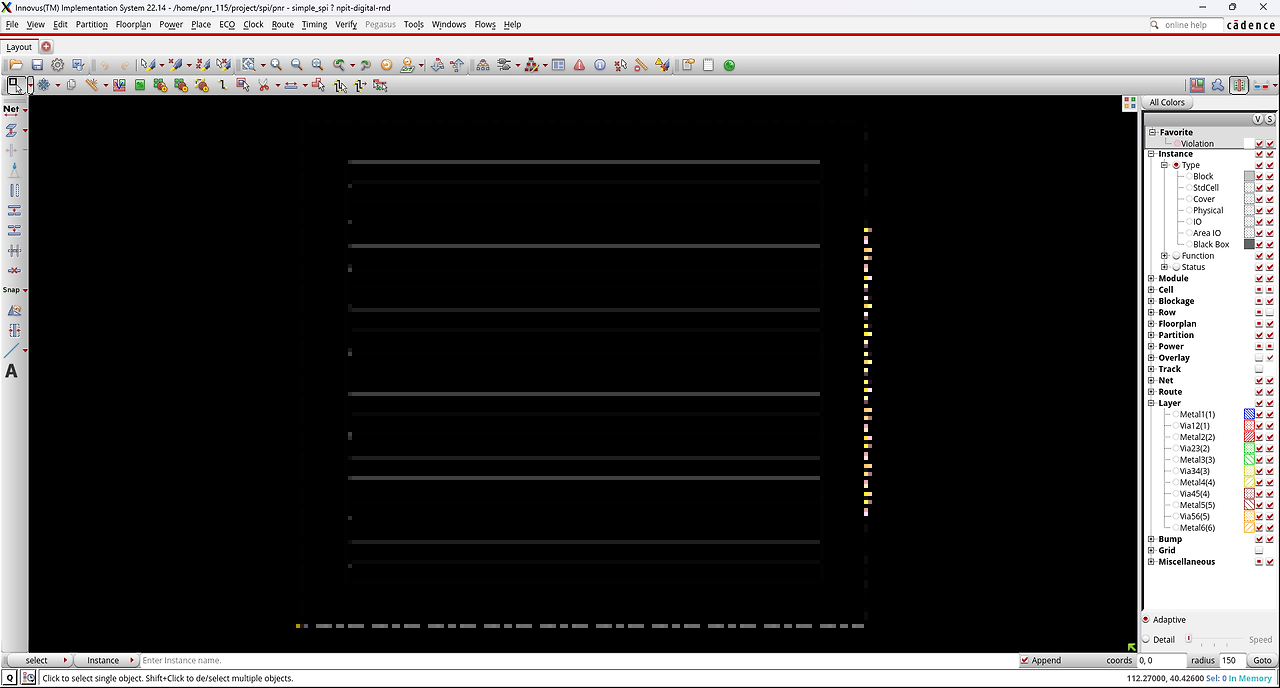

4. reg0~reg30은 spread - center에 배치

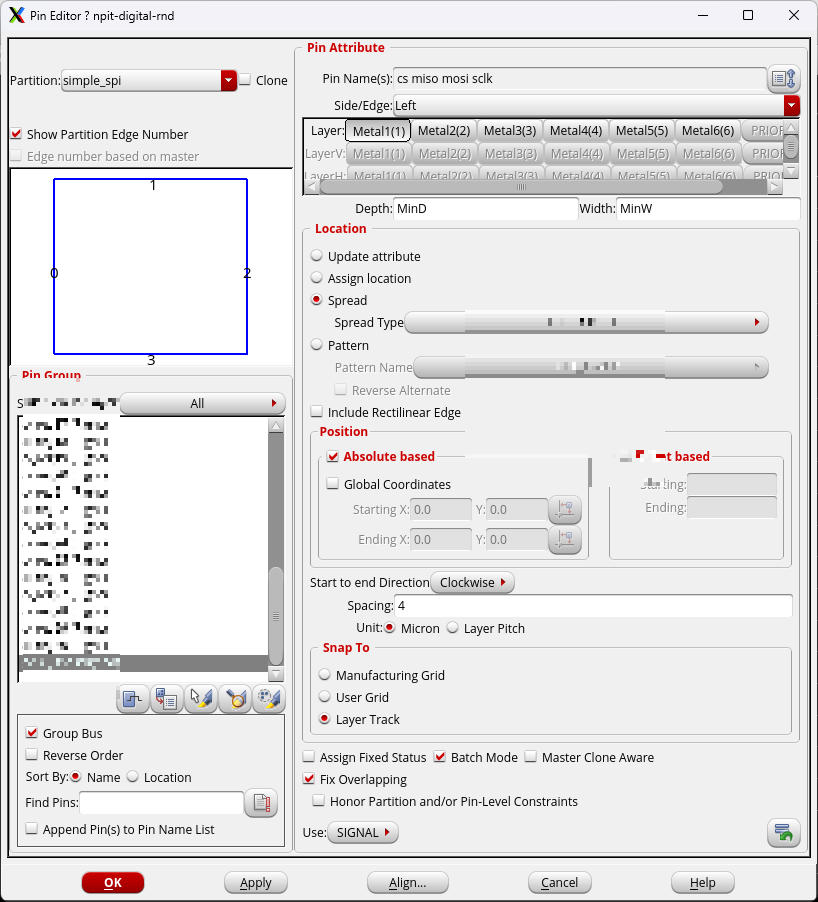

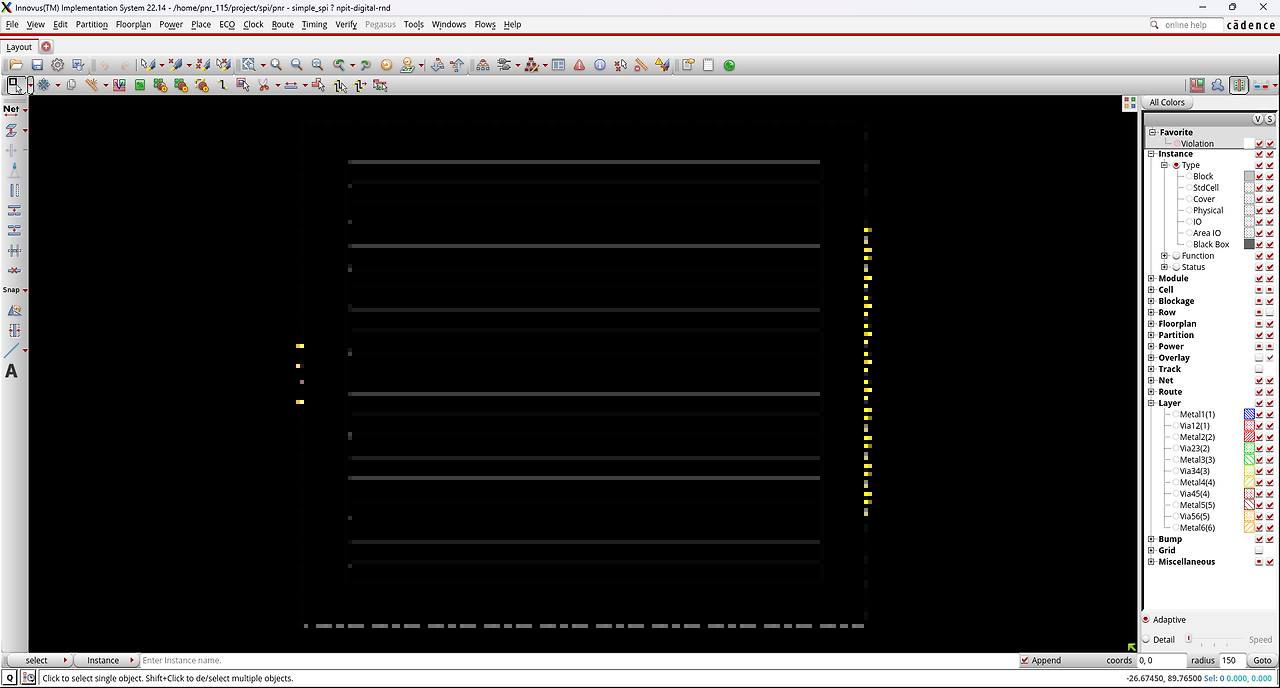

5. 나머지 핀은 왼쪽에 배치

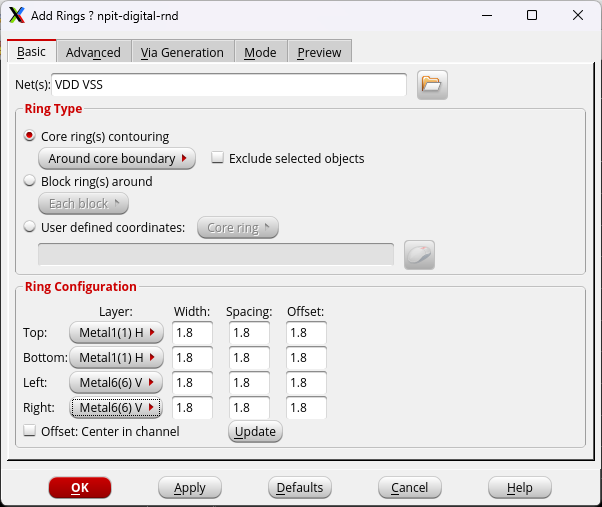

6. Power - Power Planning - Add Ring으로 실행 후 VDD VSS 입력, Width, Spacing, Offset 설정

- Width: VDD와 VSS의 선폭

- Spacing: VDD와 VSS의 간격

- Offset: Core로부터의 거리

7. Add Ring 설정 후 OK

8. Route - Special Route: 각 Cell에 Power Line을 라우팅하기 위한 작업

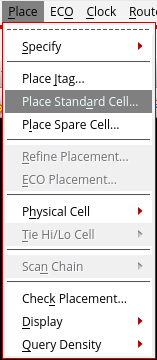

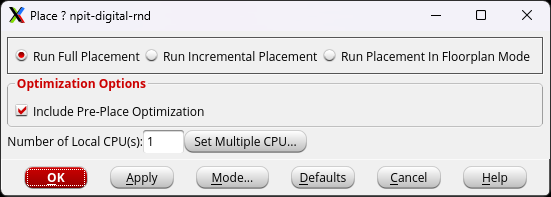

4. Placement

1. Place - Place Standard Cell

2. OK 클릭

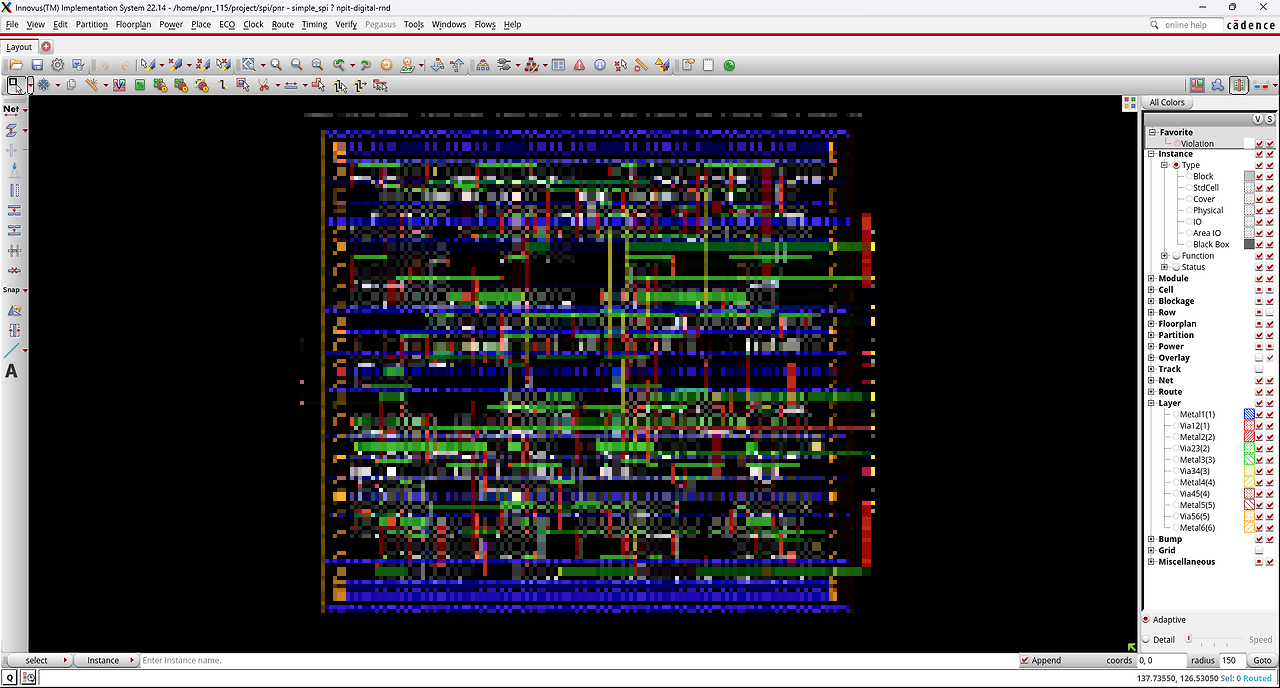

3. 결과 확인

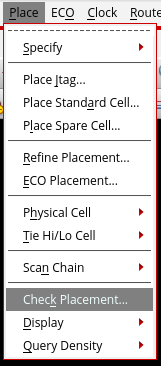

4. Place-Check Placement로 리포트 생성

5. CTS(Clock Tree Synthesis) & Route

- CTS: 모든 회로 노드에서 클럭 신호를 동일한 시간에 받을 수 있도록 하여 회로의 안정성과 성능를 보장하는 과정

- 진행 순서

- 클럭 노드 선정: 클럭 신호의 발생 지점과 도달 지점 선택

- 클럭 경로 생성: 클럭 노드 사이에 경로를 생성

- 클럭 노드 배치: 경로에 따라 클럭 노드를 배치

- 클럭 트리 라우팅: 클럭 노드 사이에 라우팅을 수행

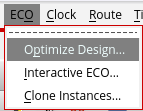

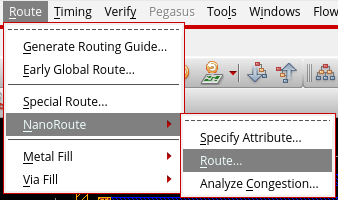

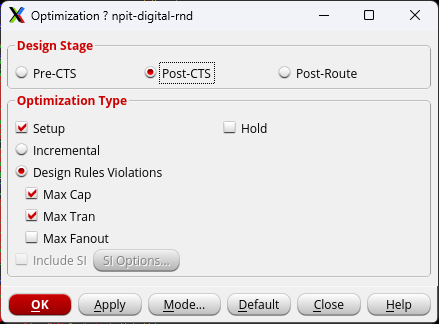

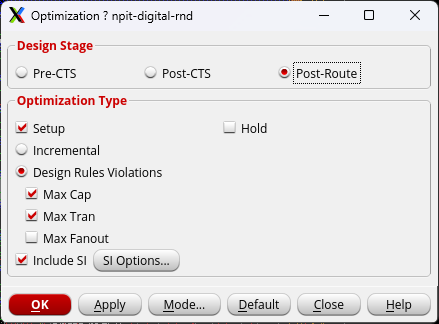

1. ECO - Optimize Design

- Pre-CTS: Routing 이전에 임의로 계산하여 CTS작업 수행

- Post-CTS: Pre-CTS 후 Routing 이후에 진행하는 CTS 작업

- Post-Route: CTS 이후 최적화 작업

2. Pre-CTS 수행 후

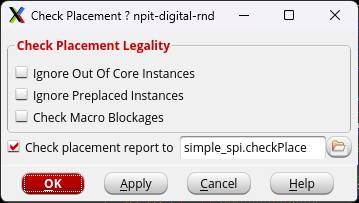

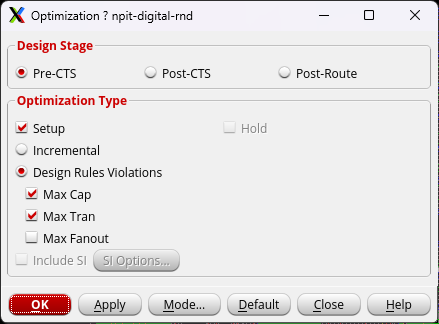

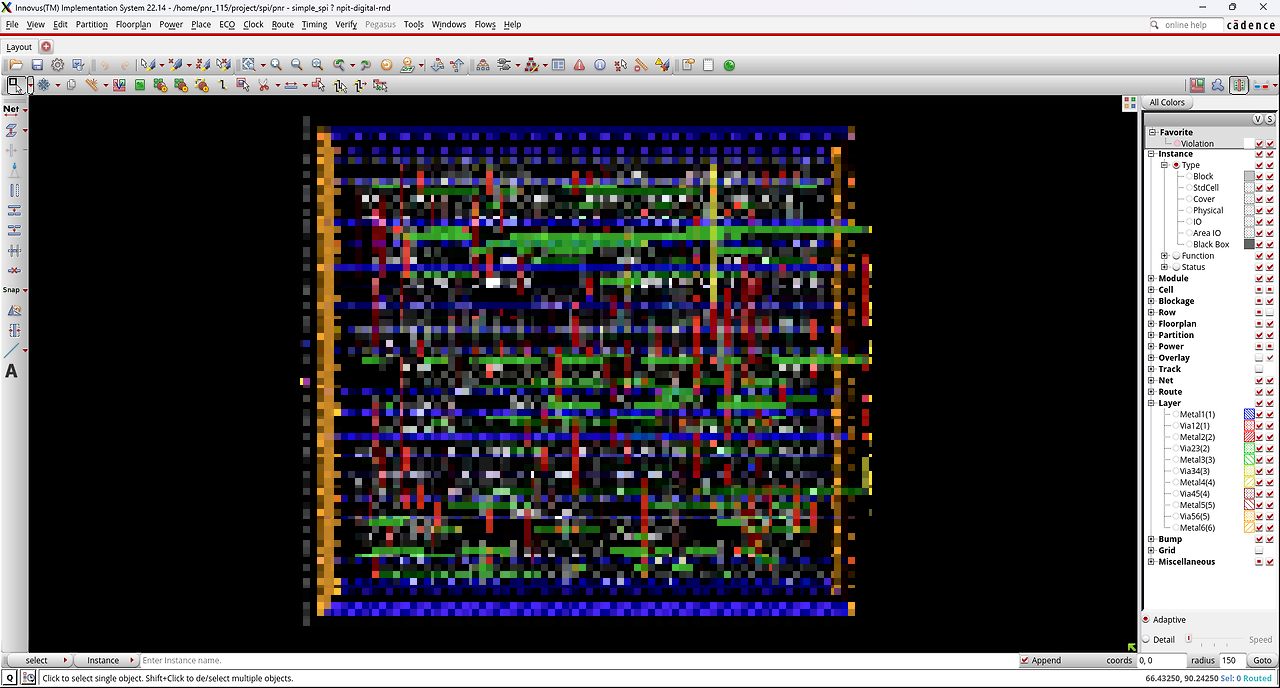

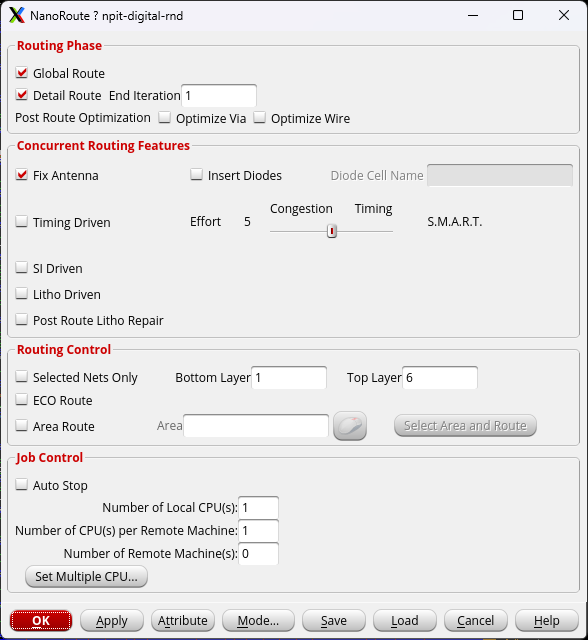

3. Route - NanoRoute - Route - OK

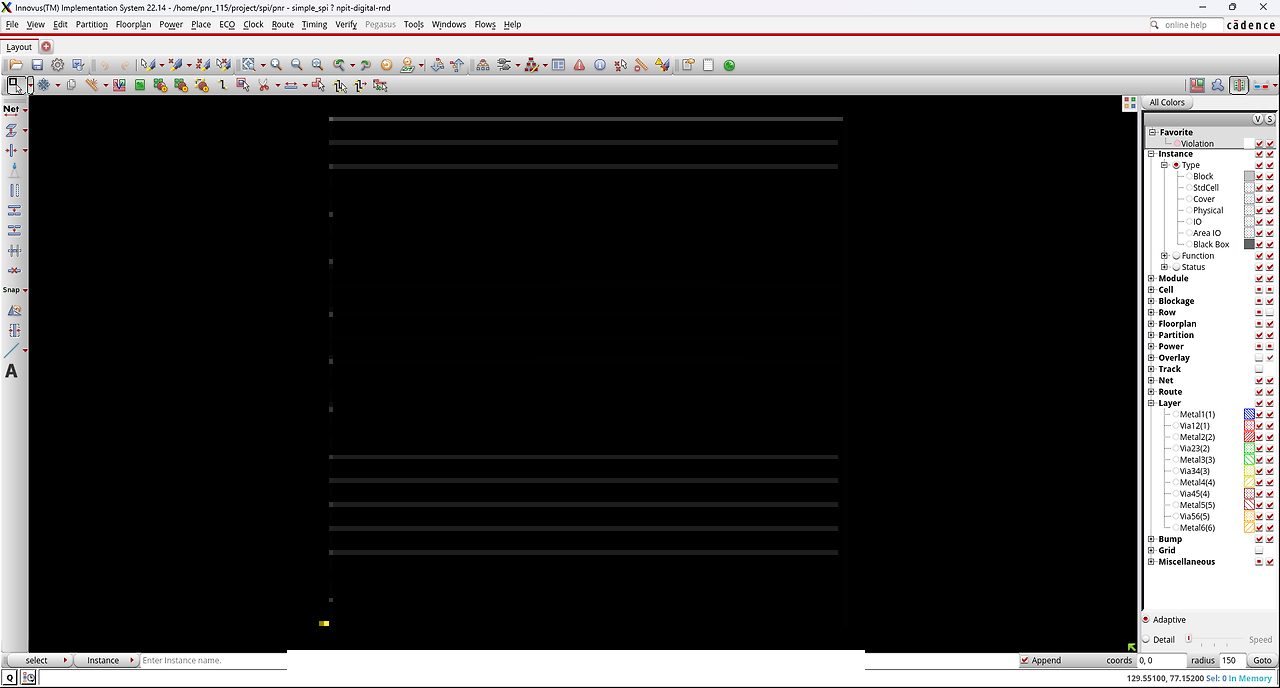

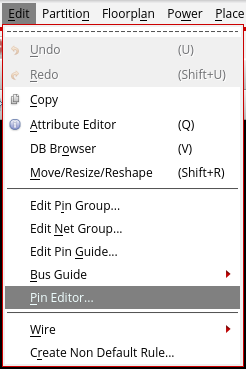

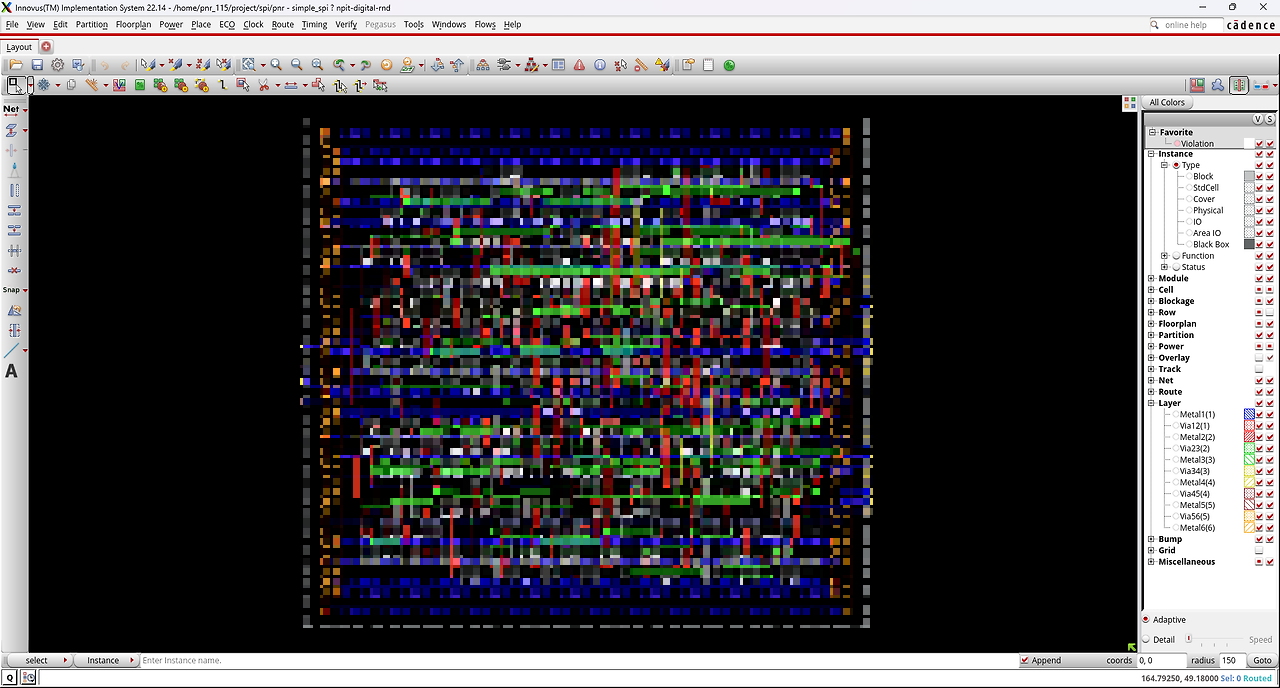

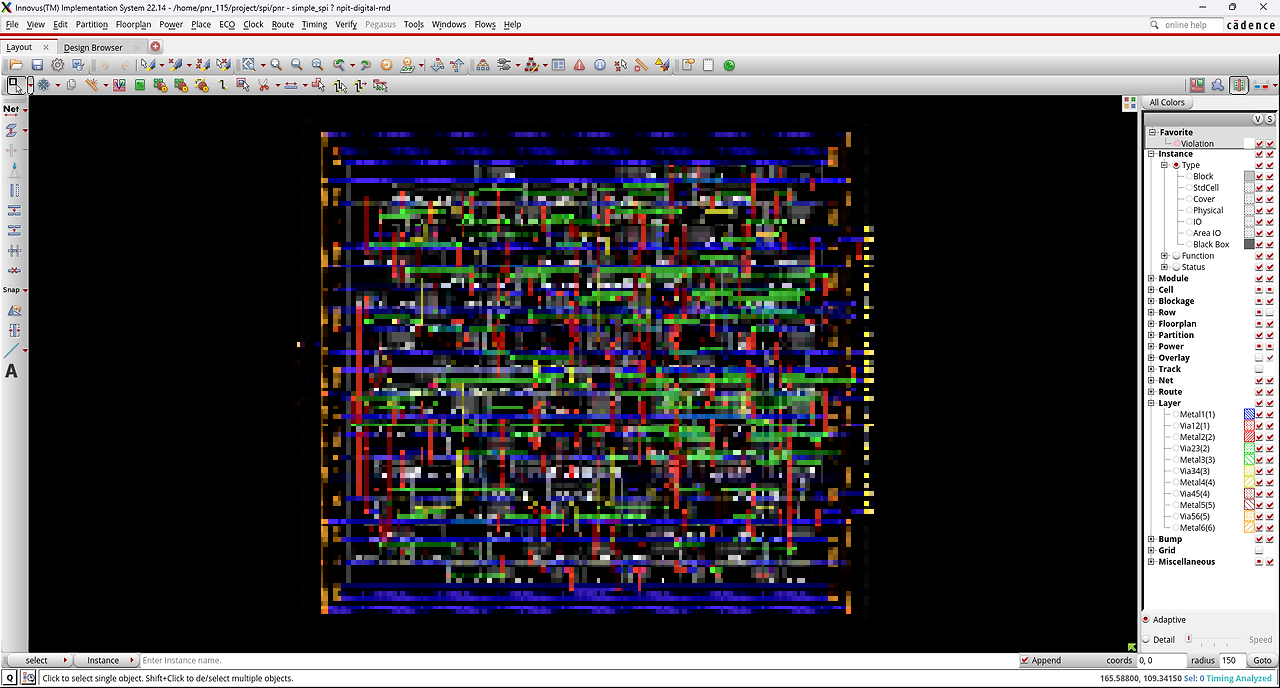

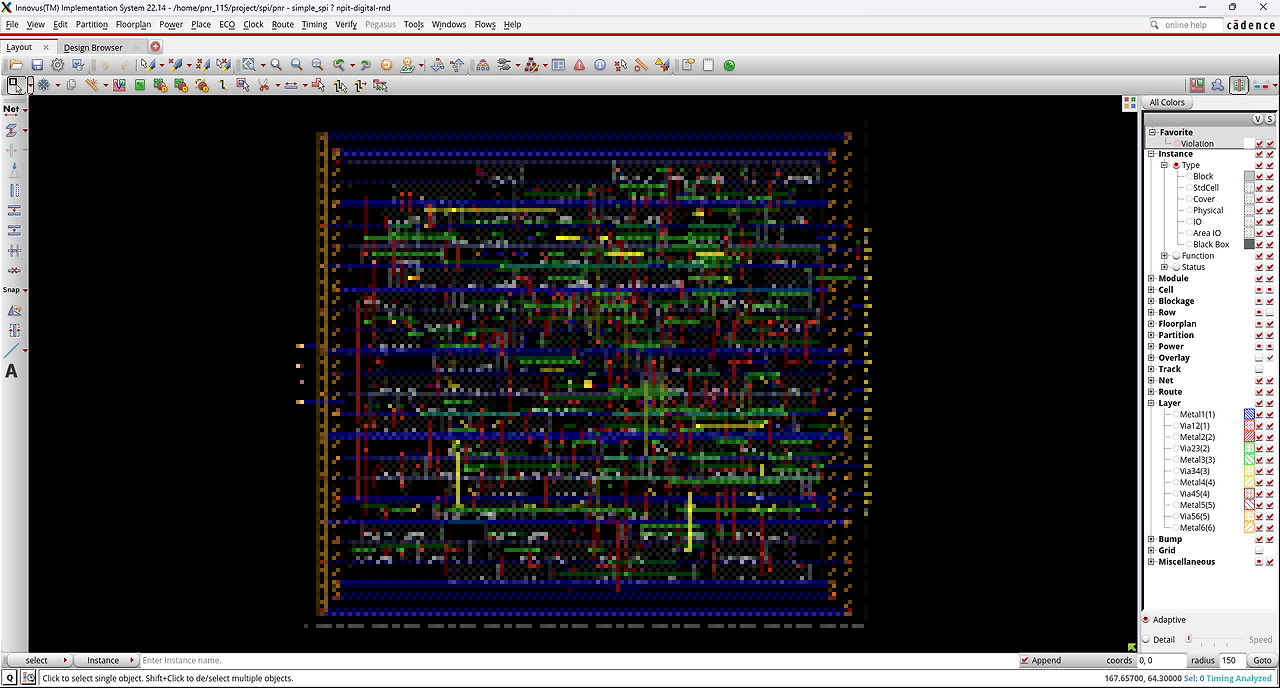

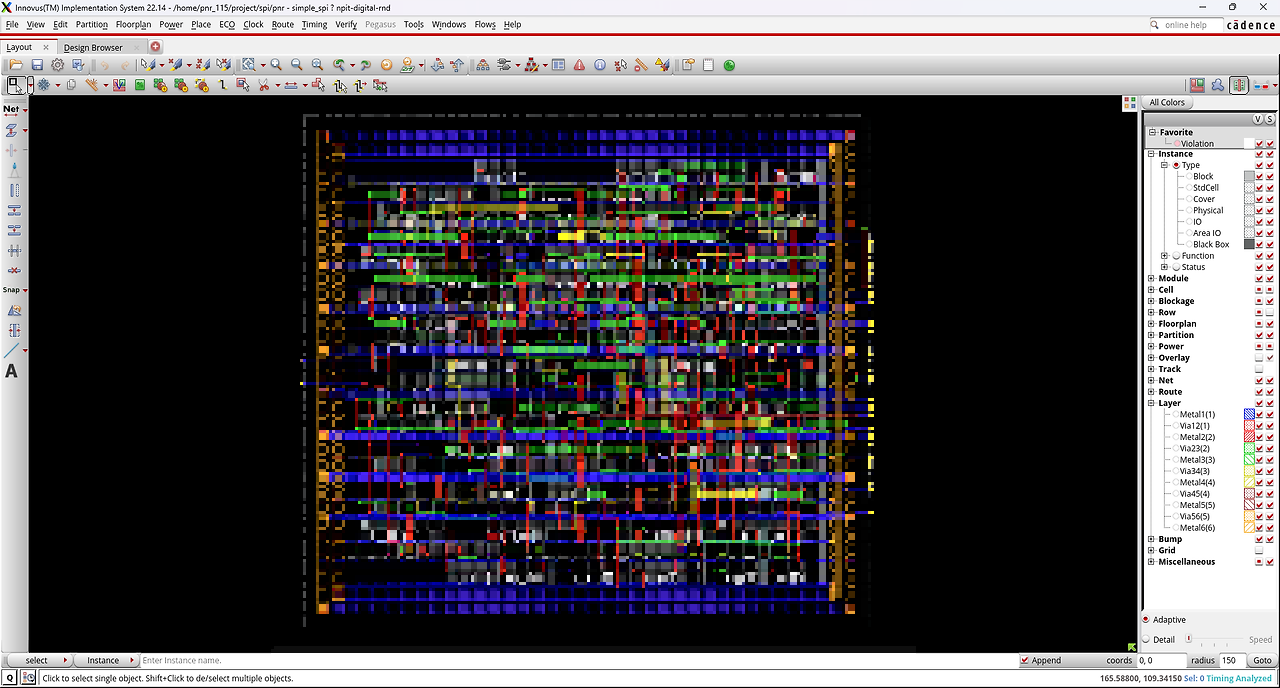

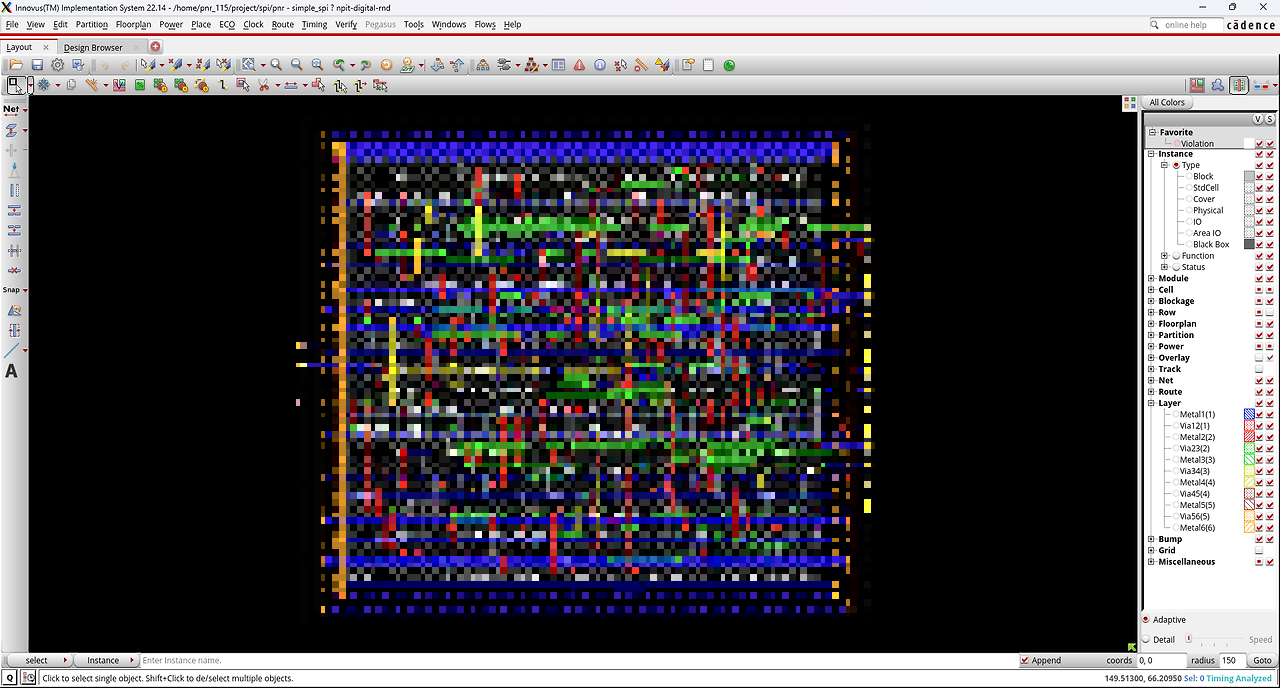

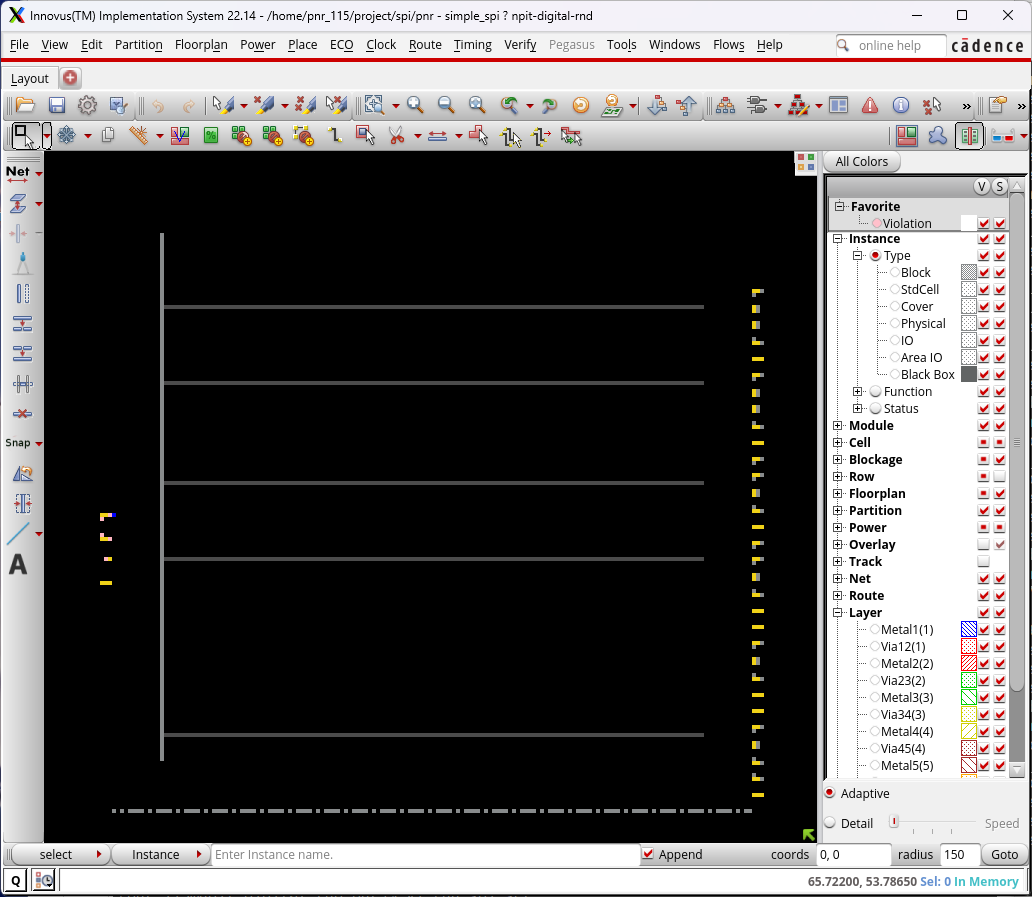

4. NanoRoute 종료 후 레이아웃

5. Post CTS 진행

6. Post CTS 진행 후 결과

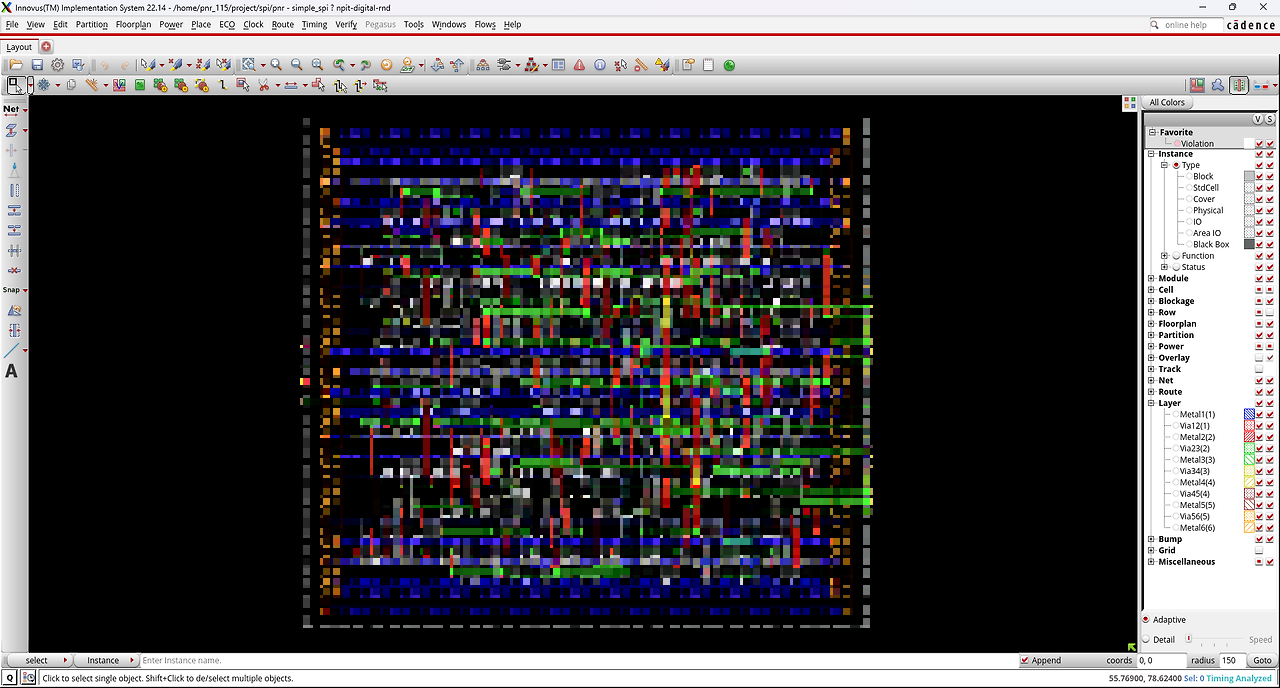

7. Post-Route 이전에 Route 생성을 다시 하기 위해 Route-NanoRoute-Route

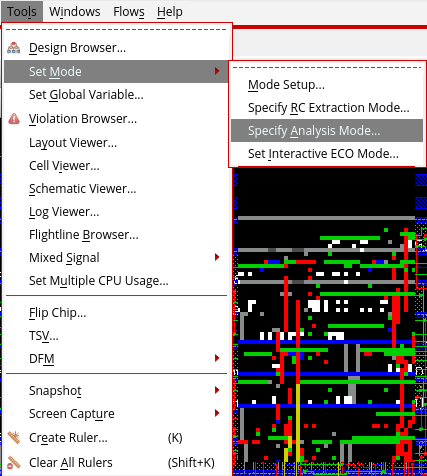

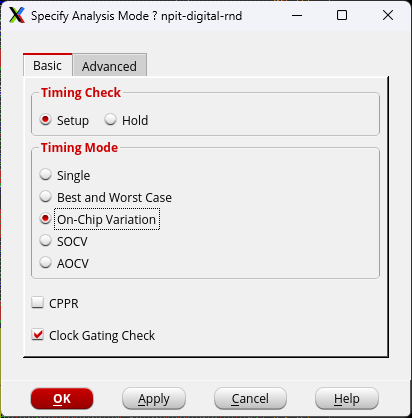

8. Post-Route 이전에 세팅값 변경을 위해 Set Mode-Specify Analysis Mode를 On-Chip Variation으로 변경

On-Chip Variation: Chip에서 Violation이 있는 지 확인하기 위한 세팅

9. 위 세팅 변경 후 Post-Route 진행

10. 실행 결과

Timing Check

1. Timing - Report Timing에서 Pre-CTS, Post-CTS, Post-Route 단계를 진행하며 각각 타이밍 확인 필요

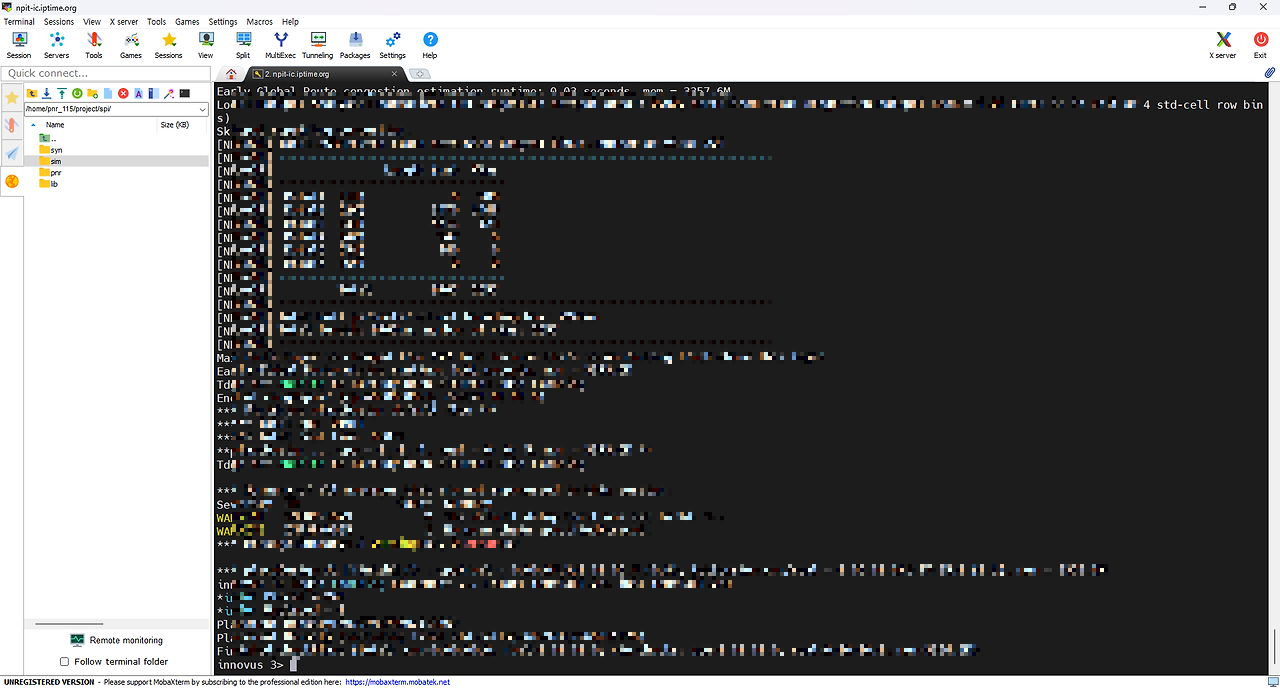

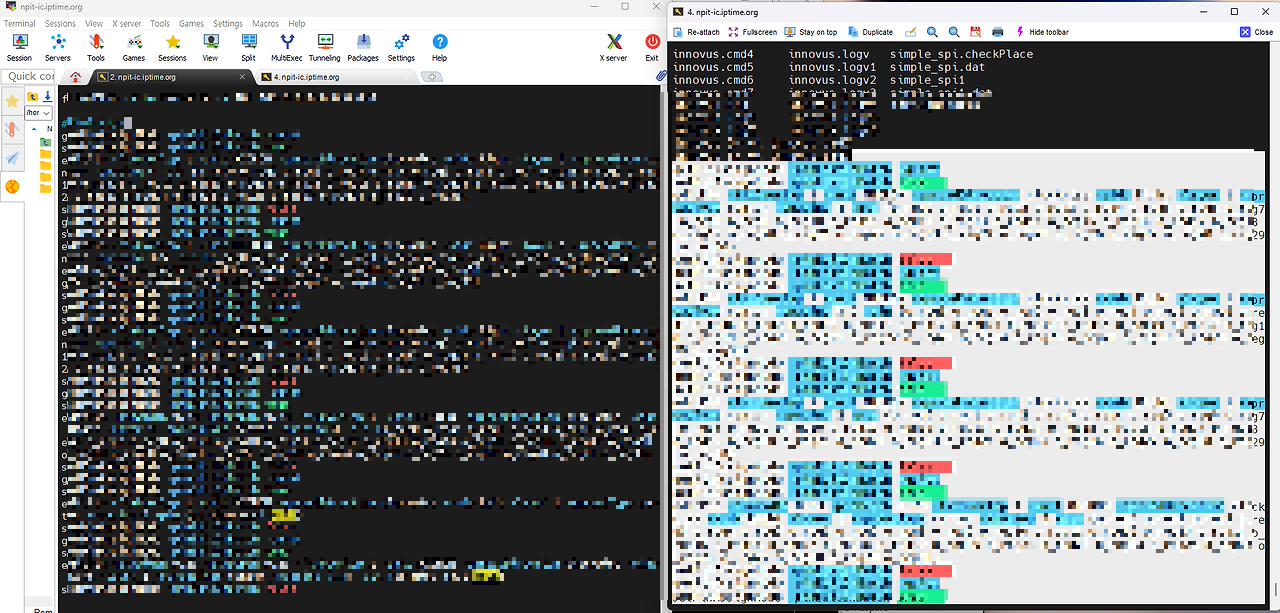

2. mobaxterm화면에서 timingReports 디렉토리 내의

gzip -d simple_spi_preCTS_all.tarpt.gz

gzip -d simple_spi_postCTS_all.tarpt.gz

gzip -d simple_spi_postRoute_all.tarpt.gz

을 입력하여 각각의 압축파일을 해제

3. mobaxterm 화면에서

vi -d simple_spi_preCTS_all.tarpt.gz

vi -d simple_spi_postCTS_all.tarpt.gz

vi -d simple_spi_postRoute_all.tarpt.gz

를 입력하여 각 파일을 열고 각 단계에서의 Stack Time 확인

4. Slack Time이 양수가 나와야 정상

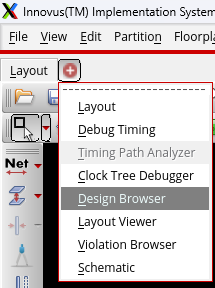

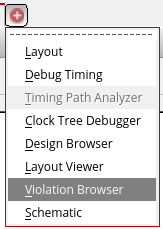

5.잘못된 부분이 있다면 해당 net을 확인한 뒤 Layout 탭 옆의 + 버튼을 눌러 Design Browser 열기

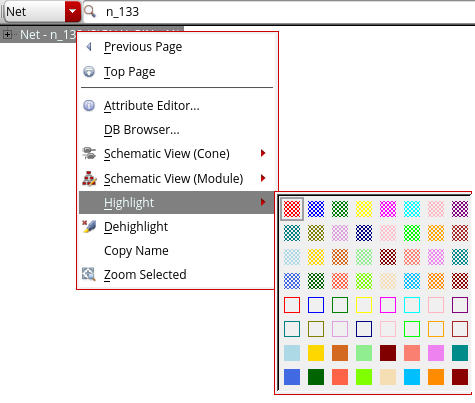

6. 잘못된 Net 번호를 확인 후 Net으로 변경해 n_번호(n은 net을 의미)입력 후 우클릭 - Highlight로 색상 변경하면 해당 net 확인 가능

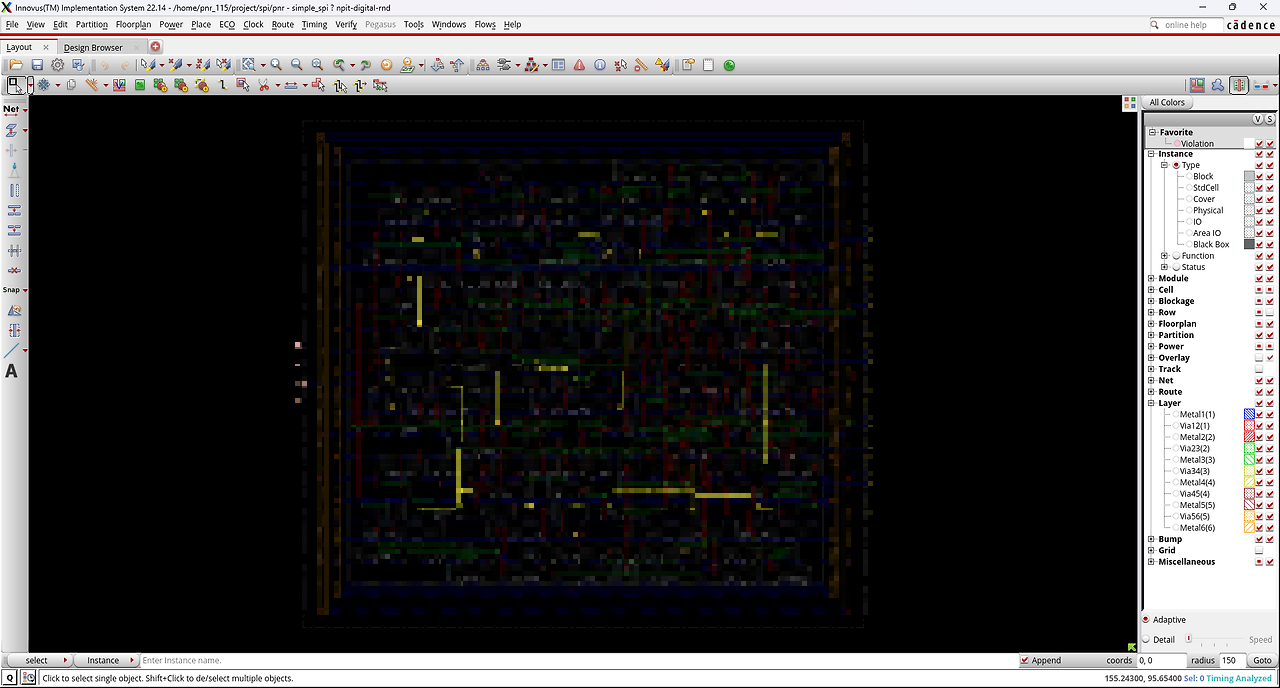

7. Layout 탭으로 돌아와서 F12 버튼 입력 시 아래 사진과 같이 표시 모드 전환

6. Filler Insert

- 빈 자리를 채우거나 없애는 과정 필요

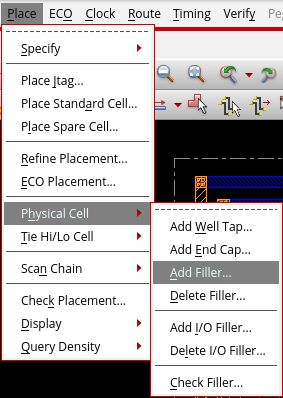

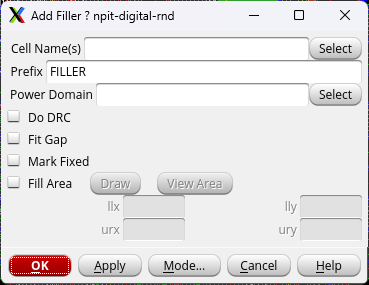

1. Place - Physical Cell - Add Filler

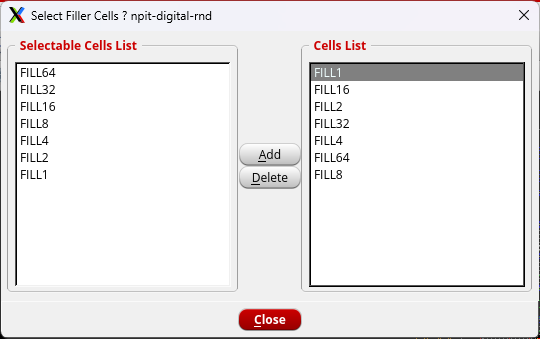

2. 필러 배치 순서는 큰 필러 -> 작은 필러 순으로 배치 권장

3. select를 눌러 필러 추가

4. close 후 ok클릭하여 필러 배치 확인

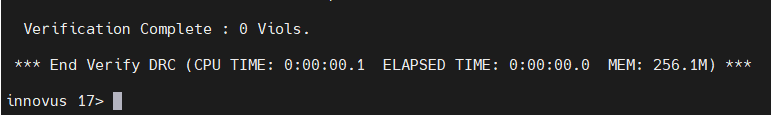

최종 단계: Verify DRC

1. Verify - Verify DRC

2. mobaxterm 창에서 0 Violations 확인

3. Violation이 발생했다면 Violation Browser 탭을 열어 확인 가능

- 우측 상단의 3D 보기를 통해 내부 회로의 Short 여부 등 확인 가능

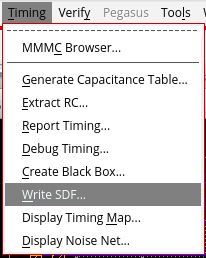

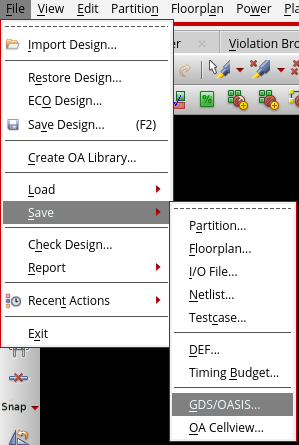

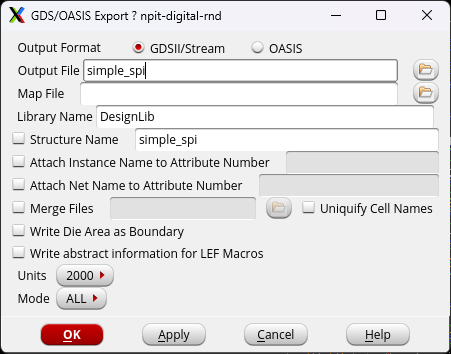

SDF, Netlist, GDSII 파일 저장

- SDF 파일과 Netlist 파일: 설계자에게 Post-Layout Simulation을 진행하기 위해 보내지는 파일

- GDSII파일: 시뮬레이션, Time Vilation / DRC 에 문제가 없으면 최종으로 설계자에게 보내지는 파일

- P&R 전후의 파일 차이

- Netlist 파일

- P&R 전: CTS 고려 X

- P&R 후: CTS 진행 후의 Netlist - SDF 파일

- P&R 전: 셀에 대한 Delay만 존재

- P&R 후: Placement&Routing의 진행으로 인해 Net Delay 정보도 포함

- Netlist 파일

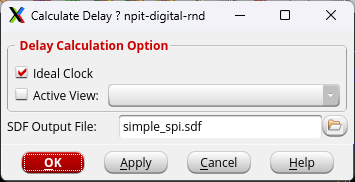

1. timing - Write SDF

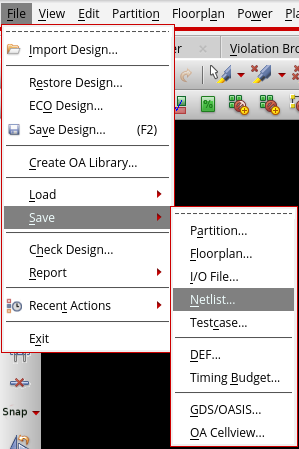

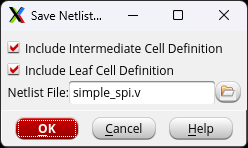

2. File - Save - Netlist

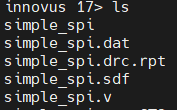

3. ls로 simple_spi.v 와 simple_spi.sdf 파일 저장 확인

4. 최종 레이아웃 파일 저장

Script파일 만들어 Design Import 진행

- 기본 생성 파일: 로그 파일, 명령 파일

- 로그 파일

- innovus.log: 기본 로그 파일

- innovus.logv: 기본 로그 파일의 상세 정보

- 명령 파일: innovus에서 수행할 작업을 지정하고 자동화하는데 사용

- innovus.cmd: 명령어를 실행하거나 스크립를 실행

1. innovus에서 innovus.cmd3파일 오픈하고 Design Import 확인 후 복사

2. innovus 폴더에 run_spi.scr 파일 생성 후 #Design Import 아래에 붙여넣기(휠클릭을 통해 붙여넣기)

3. 스크립트 파일 실행을 위해 코드 입력

4. GUI 창이 뜨지 않으면 win 입력하여 창 표시

5.Import Design를 열어 설정 확인

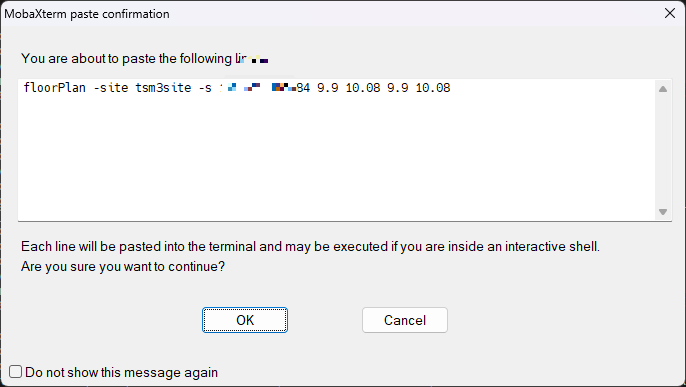

6. FloorPlan 진행: Floorplan-Specify Floorplan에 값 입력 후 저장

7.innovus.cmd 열어서 확인 후 복사 - run_spi.scr에 붙여넣기

8. Edit - Pin Editor에서 핀 설정: reg은 모두 오른쪽에, 나머지는 왼쪽에 배치

9. innovus.cmd실행하여 pin 설정 script 파일에 붙여넣기

10. Global Net Connect

11. Script로 옮기기

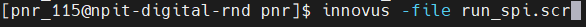

12. 중간 점검: script로 실행해서 확인해보기 ( innovus -files run_spi.scr )

13. AddRing 수행 후 Script 파일에 옮기기

14. Route - Special Route 설정 후 Script 파일에 옮기기

15. 스크립트 파일로 innovus 실행하고 정상 실행 확인

'하만(Harman) 세미콘 반도체 설계 과정' 카테고리의 다른 글

| Auto P&R 4일차 - 공개용 (1) | 2024.06.13 |

|---|---|

| Auto P&R 3일차 - 공개용 (1) | 2024.06.13 |

| Auto P&R 1일차 - 공개용 (0) | 2024.06.13 |

| Auto P&R 교육 6일차 (0) | 2024.06.02 |