Data Width: 데이터의 비트 크기를 나타낸다.

1. my_axi_test 프로젝트 생성 (board는 cora z7 선택)

2. Create Block Design - Add IP Source - Zynq 7 추가

3. Run Block Automation

4. Tool에서 Create and package New IP 에서 Next - Create ZXI4 Peripheral - Create a new AXI4 peripheral 선택 후 next - 아래와 같이 설정 후 next - finish

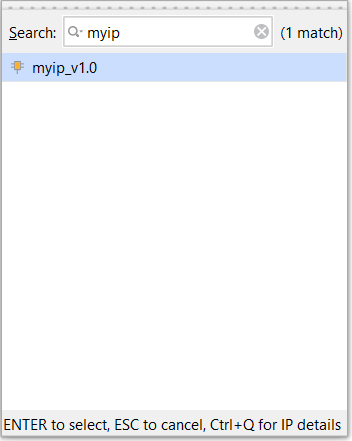

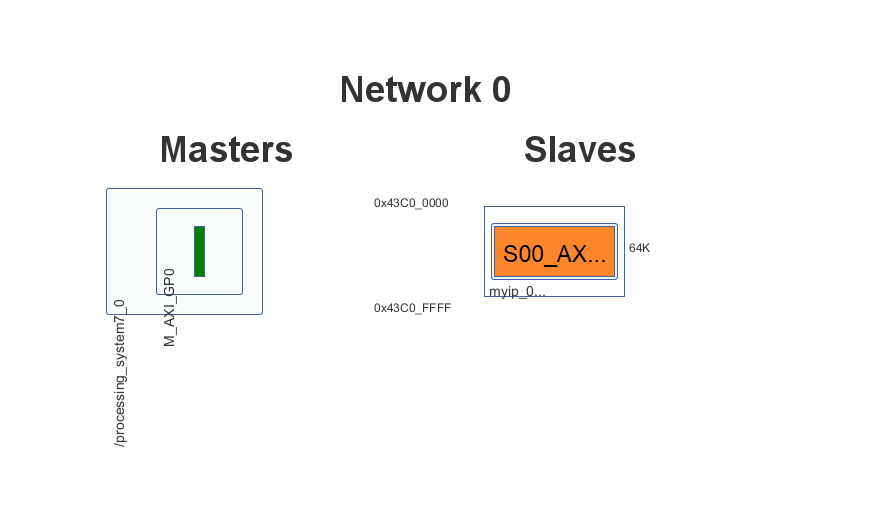

5. Add IP - 위에서 생성한 myip 추가

6. Address 확인

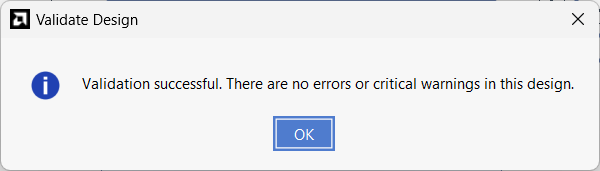

7. Validate Design

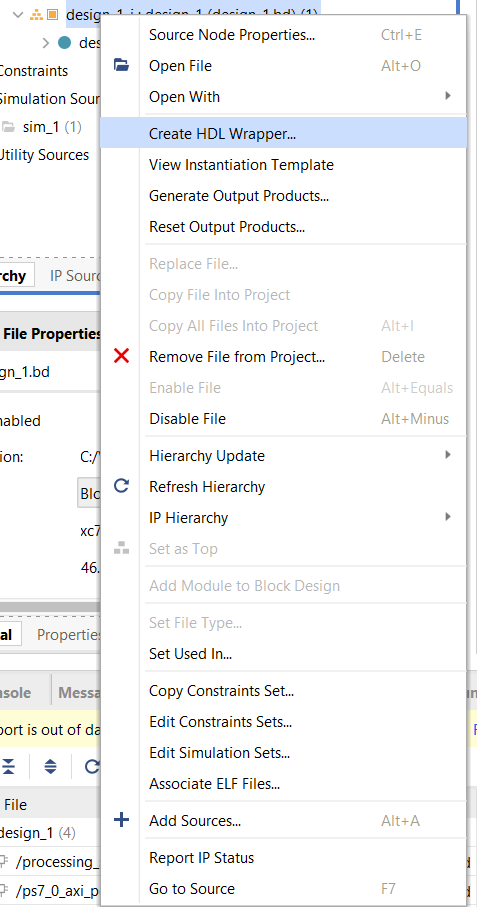

8. Create HDL Wrapper - OK

9. Generate Bitstream

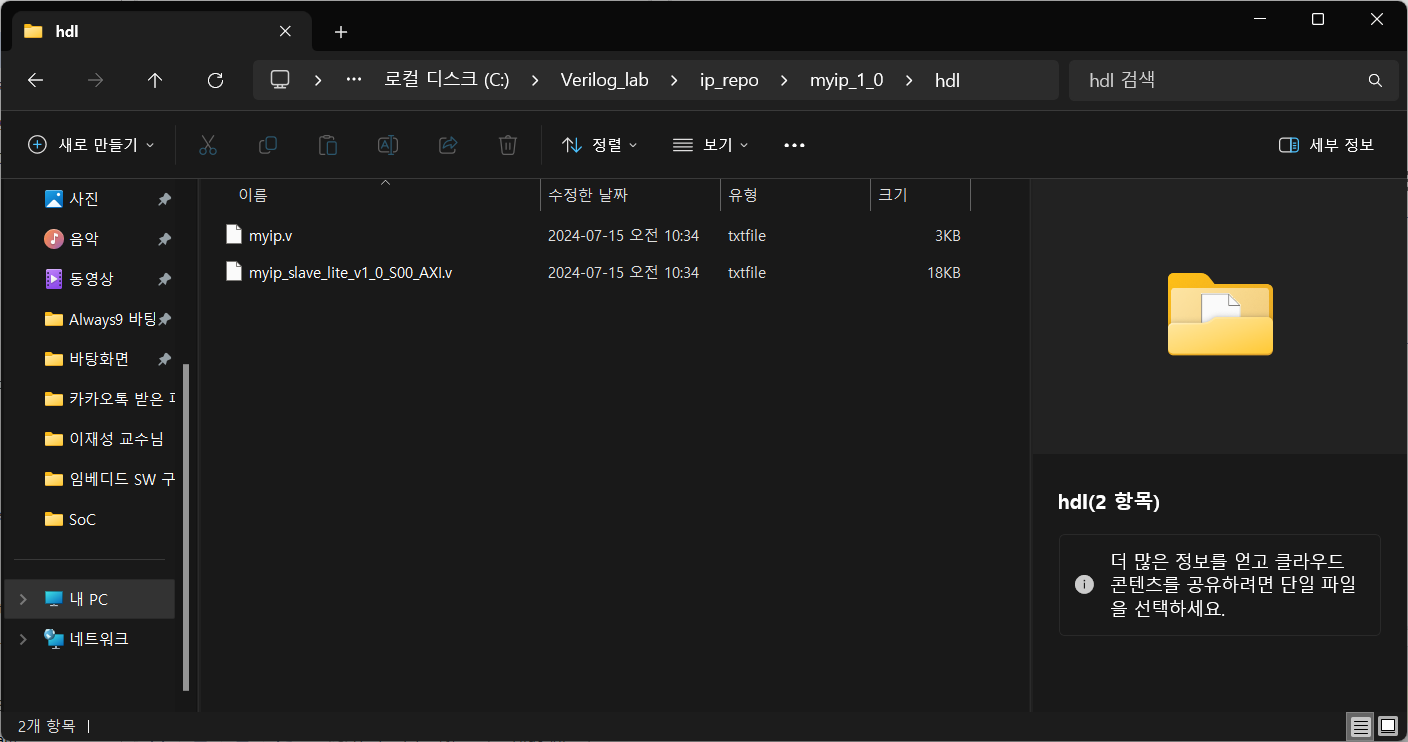

10. 프로젝트 폴더 - ip_repo - myip_1_0 - hdl에서 코드 확인

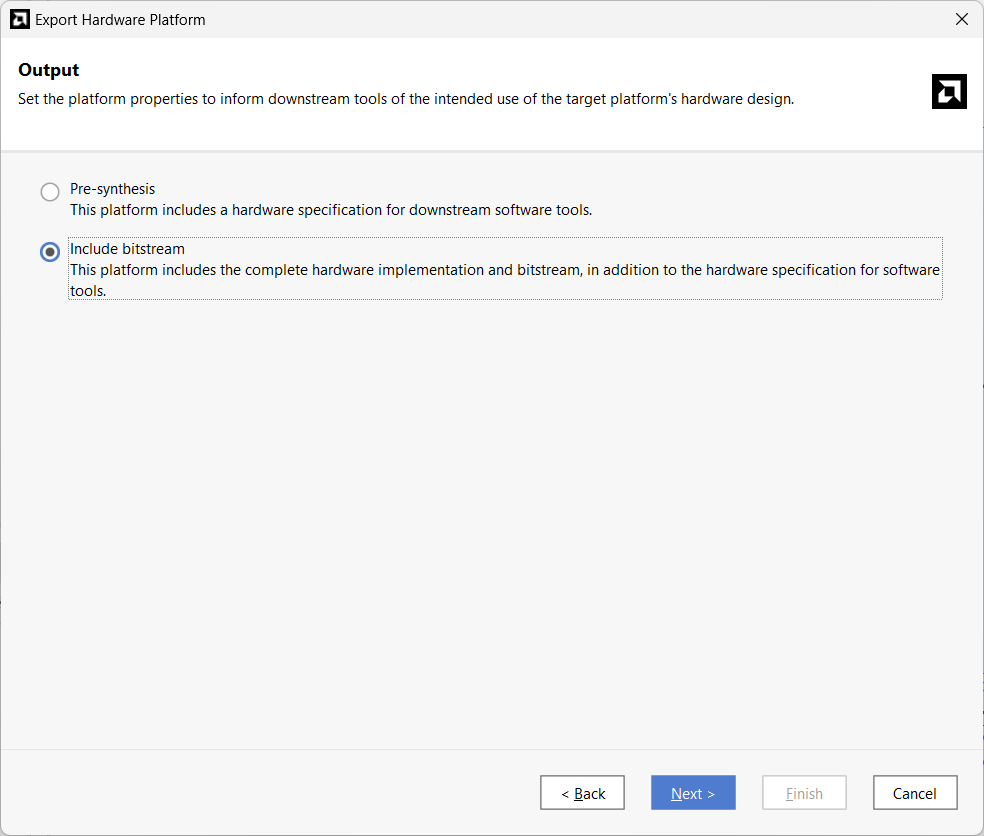

11.File - Export - Export Hardware

12. Vitis 실행

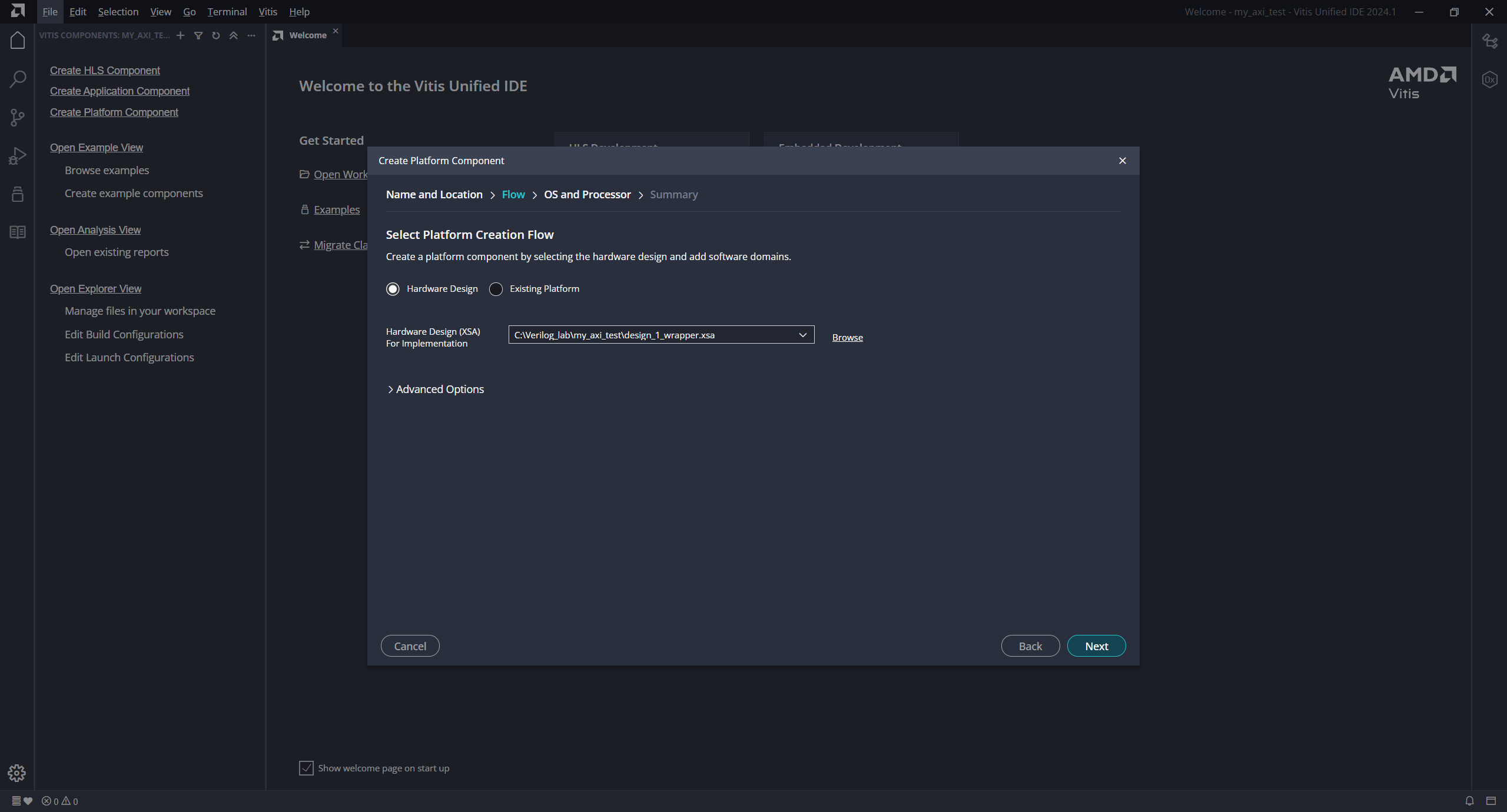

13. Open Workspace: 위에서 생성한 프로젝트인 my_axi_test 디렉토리로 설정

14. Create Platform Component

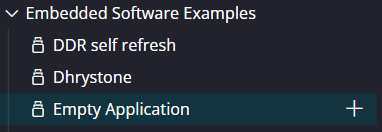

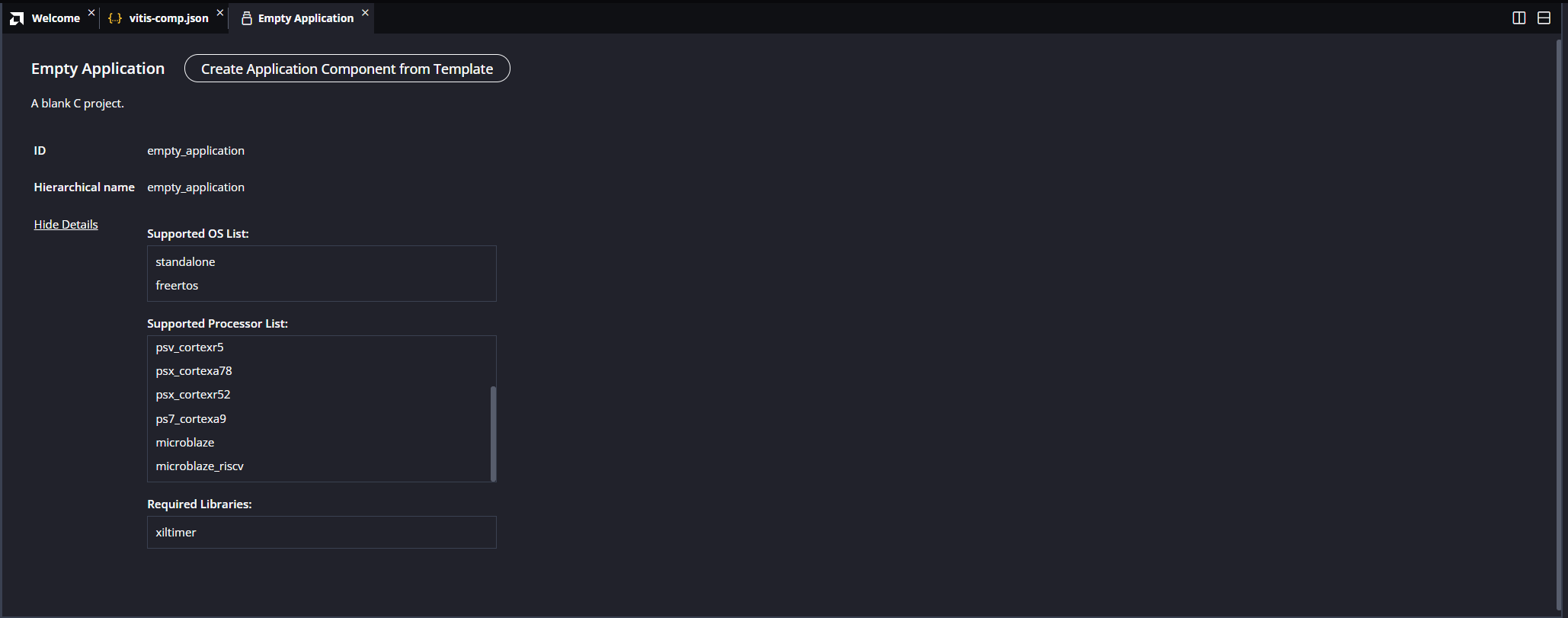

15. File - New Component - From Examples 로 생성 후 empty application - 상단의 Create Application Component from Template 선택

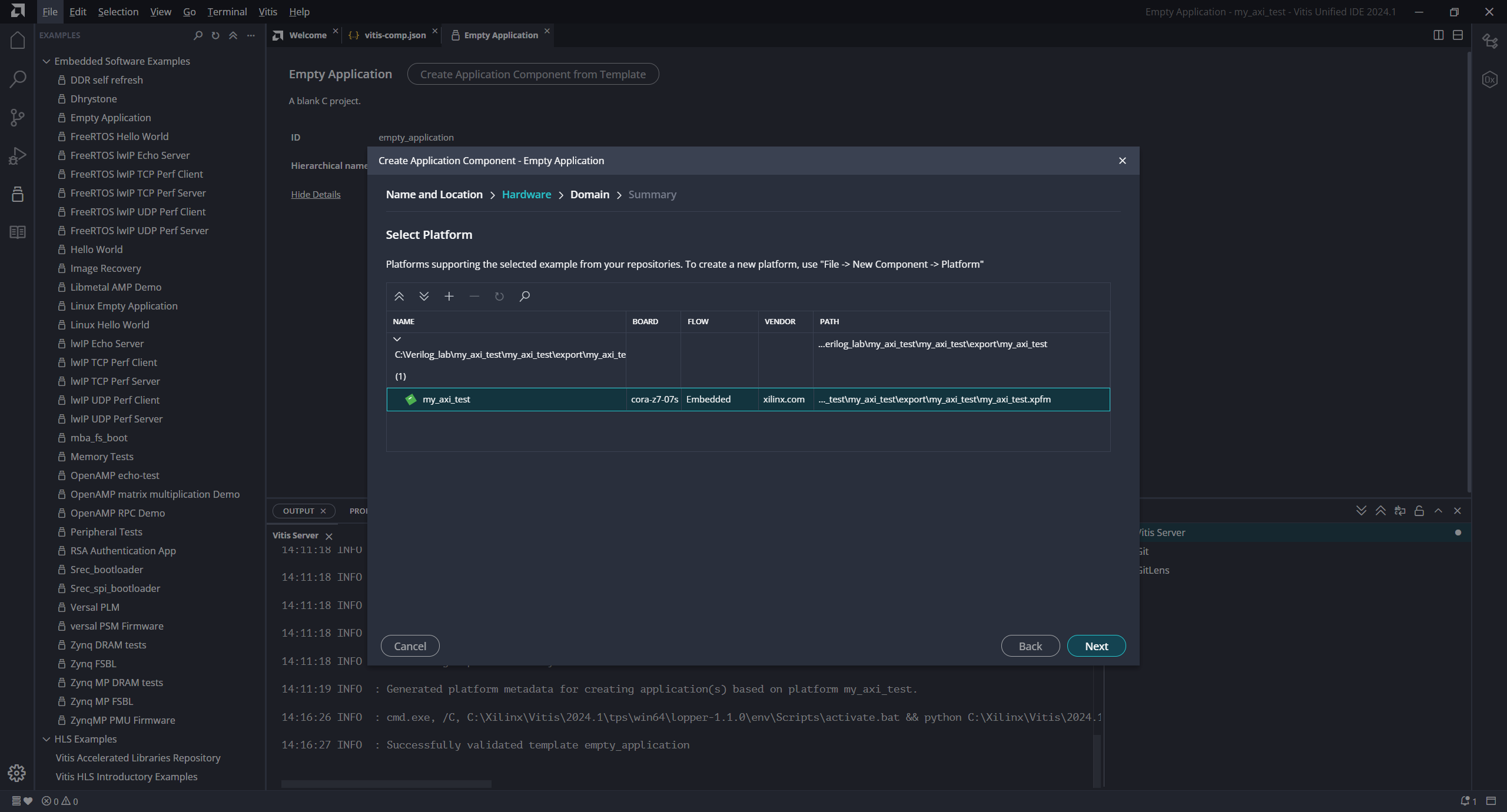

16. my_axi_test 선택 후 Next

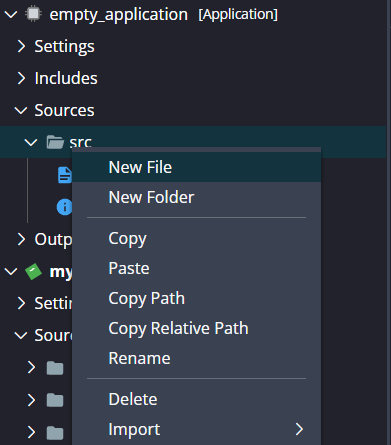

17. applicatino 우클릭 - New File로 테스트 프로그래밍 파일 test.c 만들어 코드 작성

#include "xparameters.h"

#include "stdio.h"

#include "sleep.h"

#define BASEADDR XPAR_MYIP_0_BASEADDR

#define data_num 6

int * ptr;

int main(void){

printf("AXI TEST\n");

ptr = (int *)BASEADDR;

while (1){

for (int i=0;i< data_num; i++){

*(ptr+i)=i;

printf("Write data is: %d\n",i);

sleep(1);

}

for (int i=0 ;i< data_num; i++){

printf("Read data is: %d\n",*(ptr+i));

sleep(1);

}

sleep(1);

}

return 0;

}18. Build

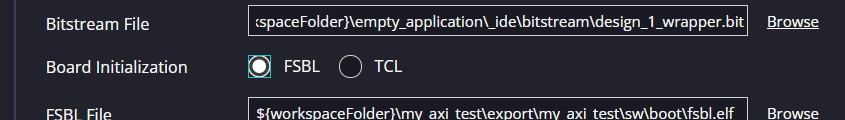

19. Component에서 application 선택 후 Run 설정에서 FSBL 선택

20. TeraTerm으로 실행 결과 확인