하만(Harman) 세미콘 반도체 설계 과정/Full Custom IC One Chip 설계

하만(Harman) 세미콘 아카데미 33일차 - Full Custom IC One chip 설계(mobaxterm 설치, 다이오드, MOSFET, NMOS, PMOS, CMOS Schematic)

semicon_designer

2024. 4. 23. 16:40

728x90

[2024.04.23.화] 인천인력개발원 하만 세미콘 아카데미

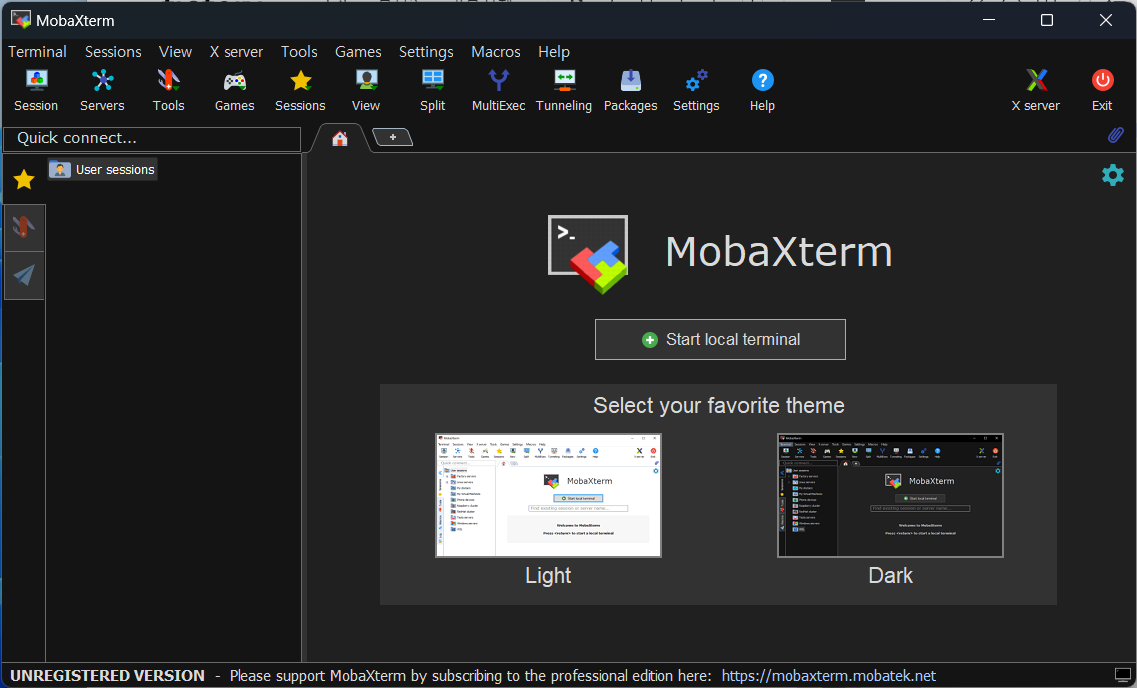

mobaxterm 설치

1. https://mobaxterm.mobatek.net/download.html 접속

2. Installer Edition 설치

3. 설치 완료

4. session - SSH 선택 후 내용 입력

5. 코드 입력

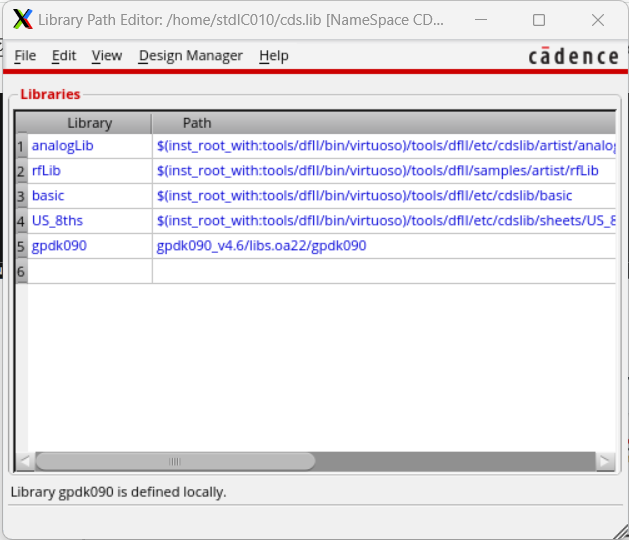

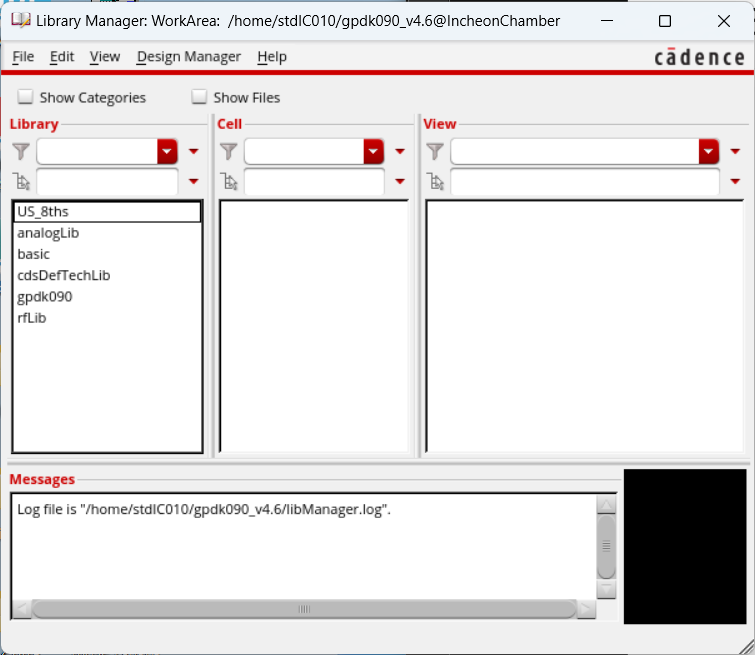

6. Tool - Library Manager, Library Path Manager 열기

7. gpdk090 Library 선택 시 다양한 소자 확인 가능

PN junction & MOSFET

1. Introduction

- IC(Integrated Circuits): 집적 회로. 많은 트랜스터가 있는 칩

- VLSI: Very Large Scale Integration

2. Doping(도핑)

- 순수 반도체 실리콘에 Dopant를 추가하는 과정

- 도핑을 통해 전도성 증가

- 5족 원소 추가: n-type 반도체(전자 개수 우세)

- 3족 원소 추가: p-type 반도체(정공 개수 우세)

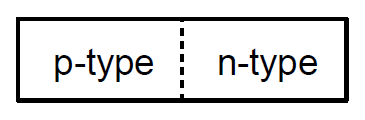

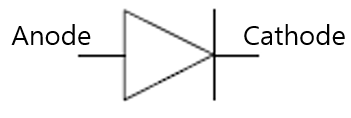

3. p-n junction

- p-type 반도체와 n-type 반도체의 접합

- 전류의 흐름은 p-type -> n-type 으로만 가능

- 전류의 흐름: Anode -> Cathode

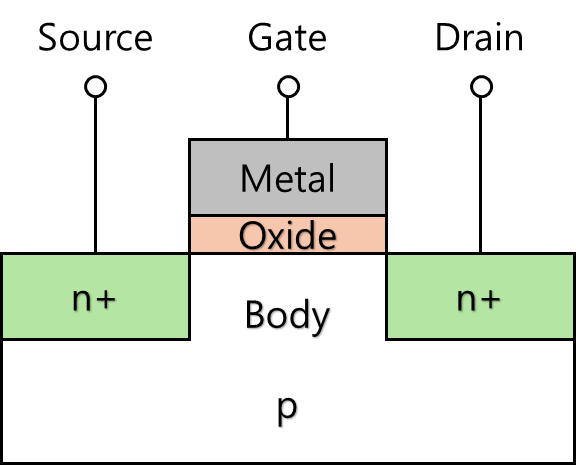

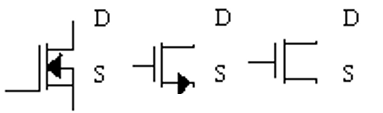

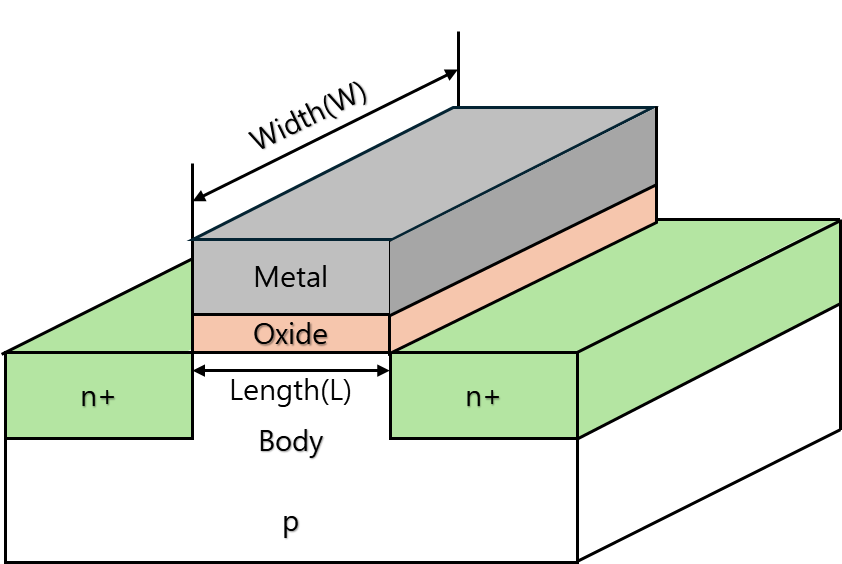

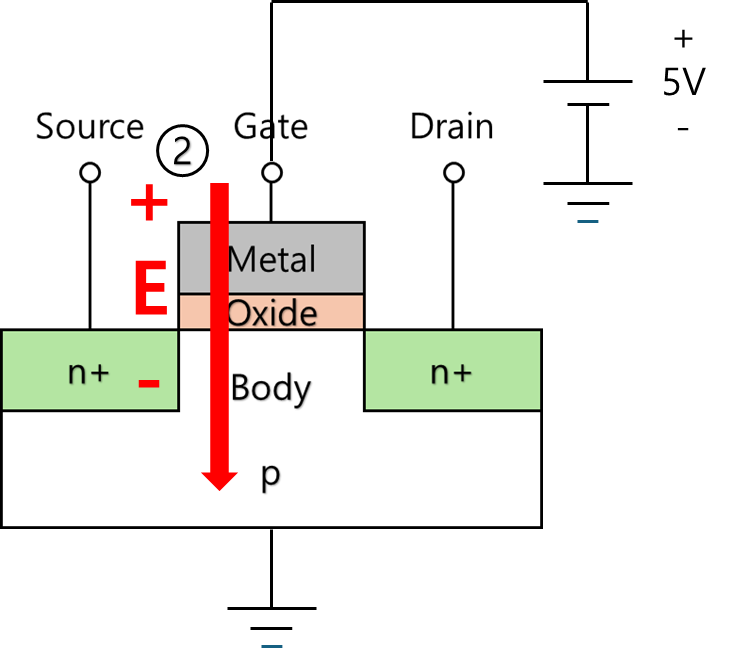

4. MOSFET: Metal Oxide Semiconductor Field Effect Transistor

- 종류: NMOS, PMOS

- 구성: Gate, Source, Drain, Body

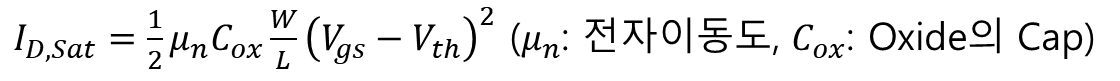

4-1. NMOS(N-type MOSFET)

- Body: 일반적으로 GND(0V)에 연결

- Gate: 0V면 Field Effect 형성 X -> NMOS OFF / 5V면 NMOS ON

- Oxide: SiO2, 두께 단위로 옴스트롱(Å = 10^-10m) 사용

- 드레인전류(I_D)를 높이기 위해 변경 가능한 값: Width(W)

- 전자 이동도, Cox는 상수

- Vgs와 Vth는 동작전압이 미리 결정되므로 변경 불가

- L은 xnm 공정에 따라 최소값 결정

- W 증가를 통해 드레인전류 상승 가능

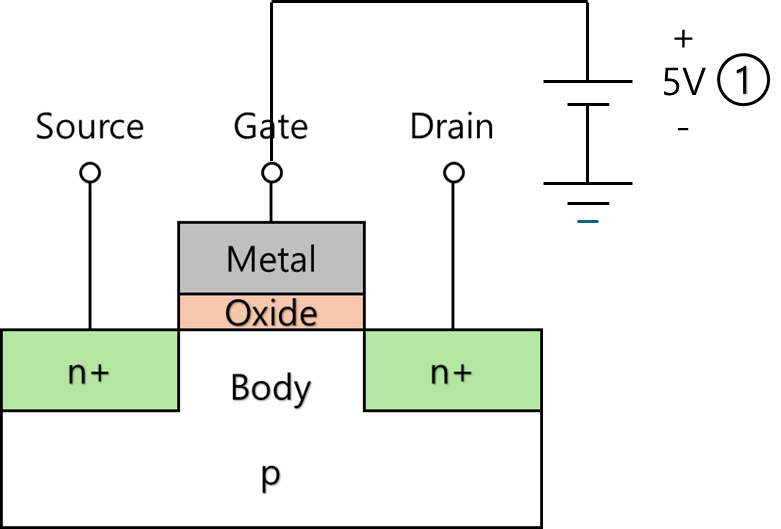

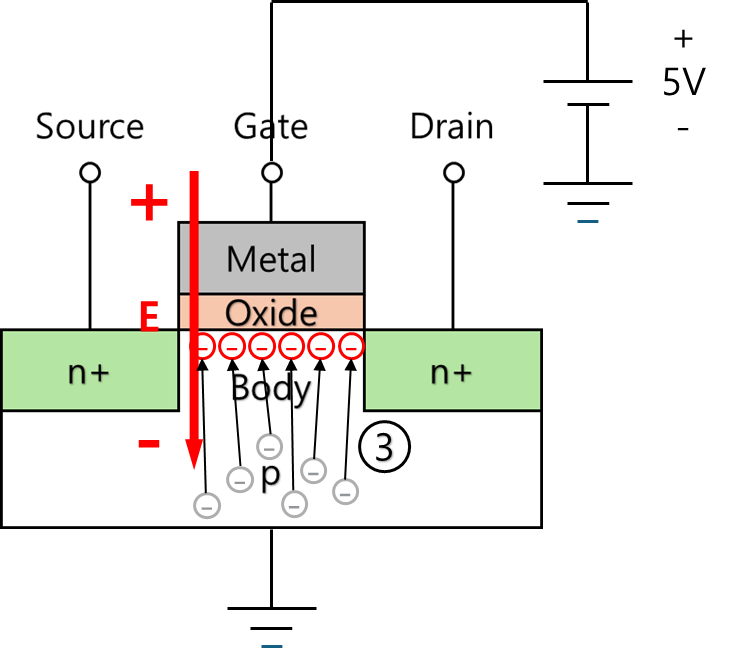

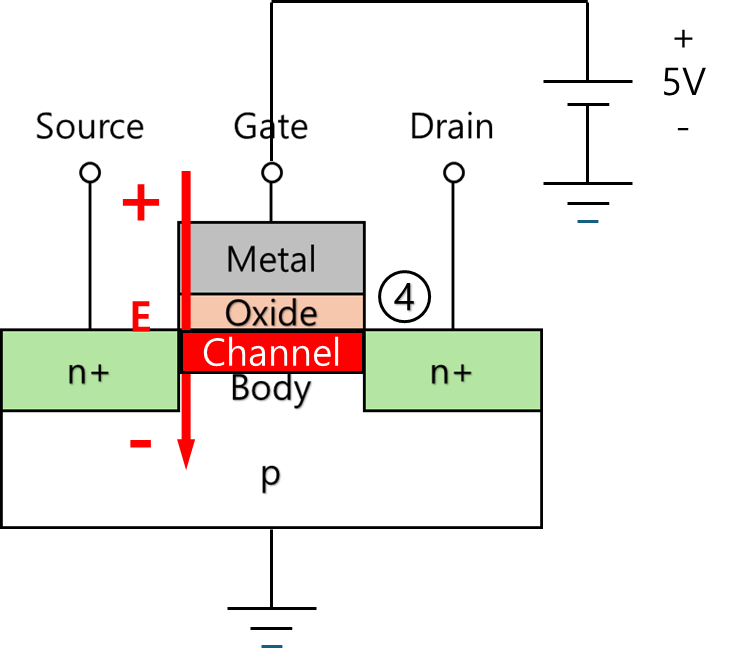

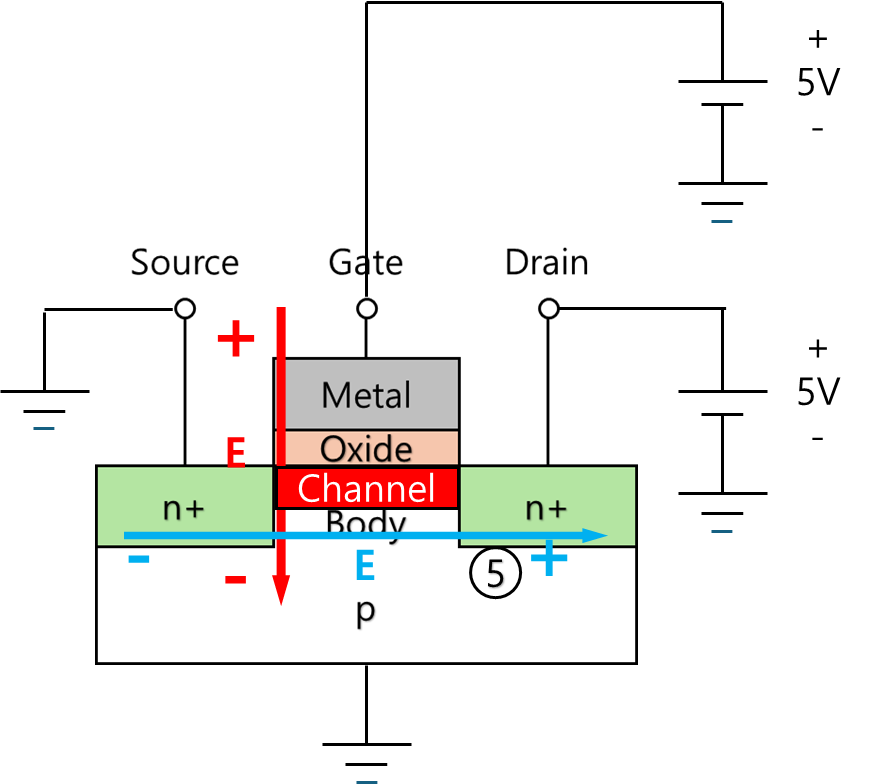

- NMOS 동작 방식

- Gate에 HIGH(5V) 인가

- 전계 형성(Field Effect)

- 전계에 의해 Oxide 아래에 전자 모임 (수직 전계에 의해 Body의 전자만 이동)

- 전자에 의해 Channel 생성(Vth 이상의 수직 전계에서 생성) - 전자에 의한 Channel이므로 n-Channel, NMOS

- Source에 0V, Drain에 5V 인가 시 수평 전계 형성

- 전자가 Source -> Drain으로 이동(전류 흐름)

4-2. PMOS(P-type MOSFET)

- NMOS와 반대로 동작

- Body에 5V 인가, Gate 0V -> PMOS ON

- 전류를 흐르게 하려면 Source에 5V, Drain에 0V 인가

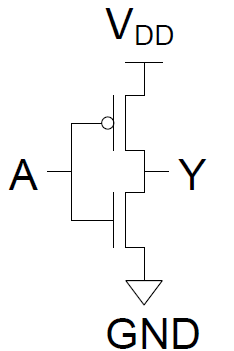

5. CMOS Inverter(NOT Gate)

- NOT Gate를 CMOS로 표현하면 다음과 같다

- A = 5V -> PMOS OFF, NMOS ON -> Y = 0V

- A = 0V -> PMOS ON, NMOS OFF -> Y = 5V

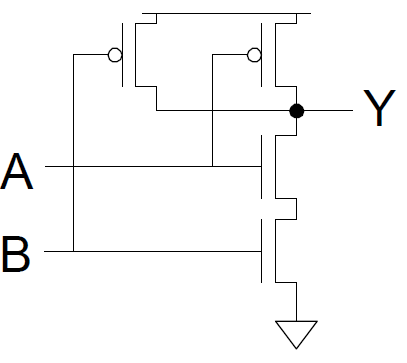

6. CMOS NAND Gate

- NAND Gate를 CMOS로 표현하면 다음과 같다

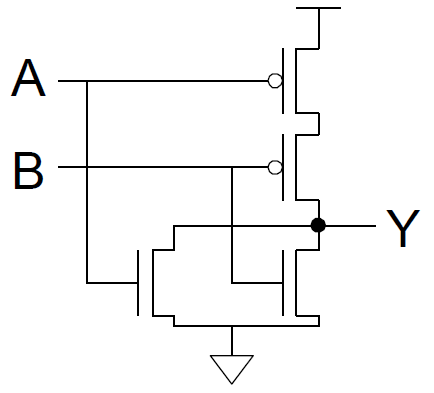

7. CMOS NOR Gate

- NOR Gate를 CMOS로 표현하면 다음과 같다

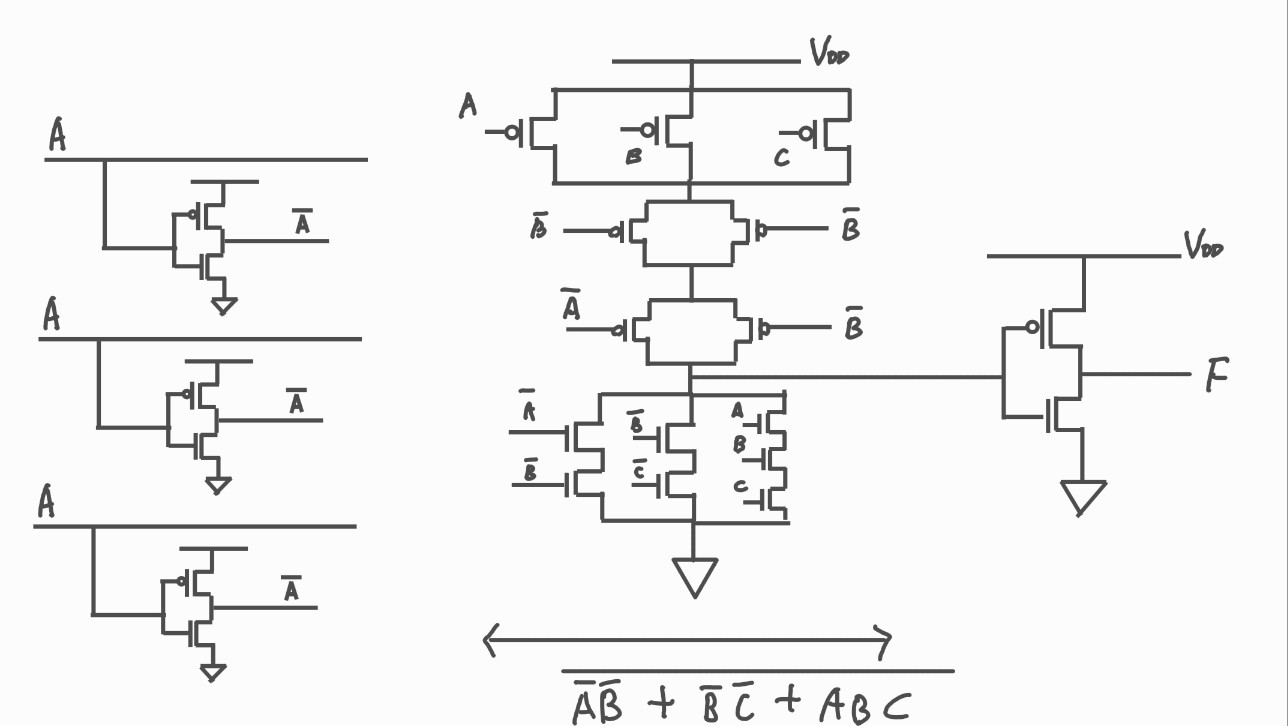

8, 위와 같이 CMOS를 이용하여 NAND, NOR 게이트를 표현하는 방법: CMOS Schematic

- F=~Y일 때

- Y가 AND연산이면 NMOS끼리 직렬연결, PMOS끼리 병렬연결

- Y가 OR연산이면 NMOS끼리 병렬연결, PMOS끼리 직렬연결

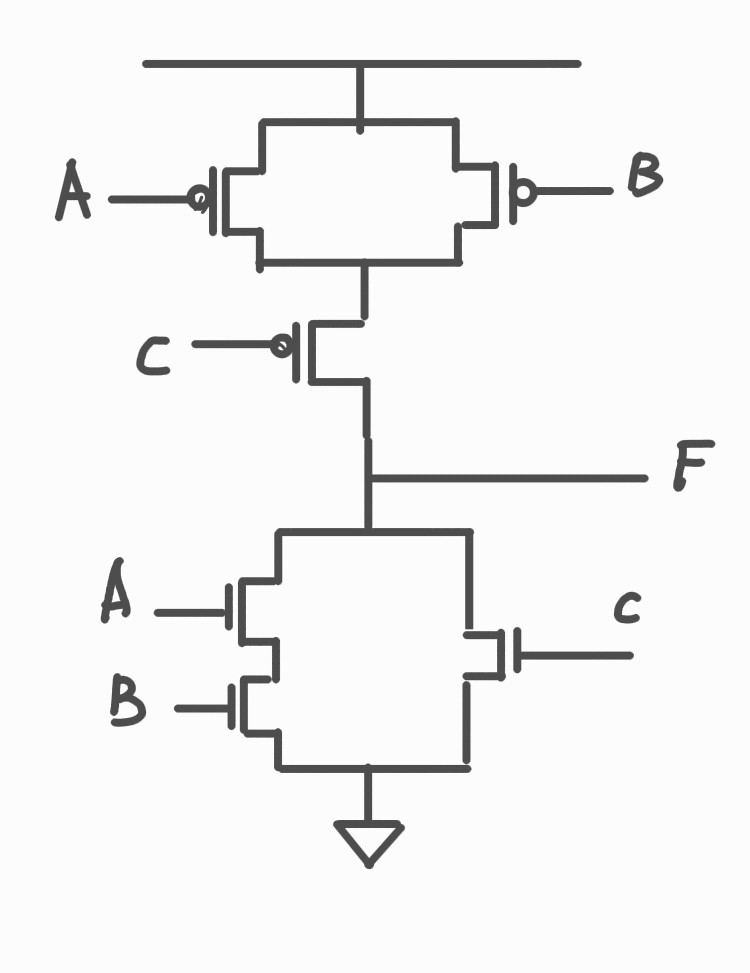

- Example1: F = ~(A*B+C)

1. A와 B를 입력으로 하는 NMOS끼리 직렬, PMOS끼리 병렬연결

2. C를 입력으로 하는 PMOS를 앞의 PMOS에 직렬, C를 입력으로 하는 NMOS를 앞의 NMOS에 병렬연결

- Example 2: F = ~(A*B+C*D)

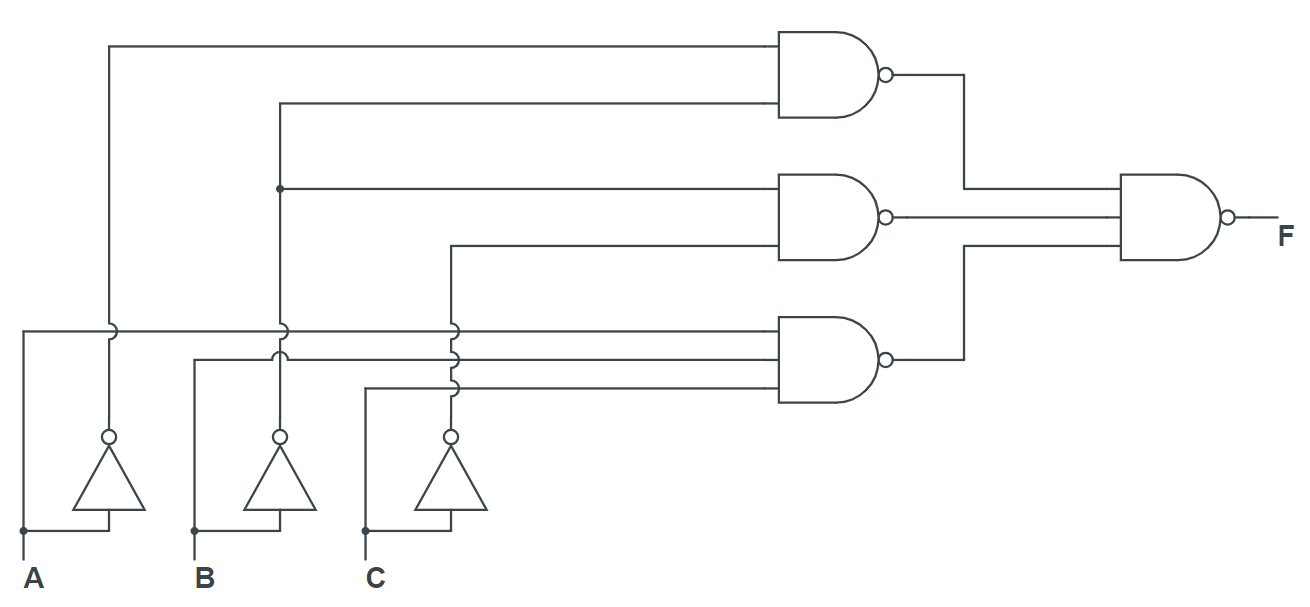

- Example 3: 다음 회로의 CMOS Schematic 구성

- Example 4: 다음 회로의 CMOS Schematic 구성

728x90